# Product Document

Published by ams OSRAM Group

## Datasheet

DS000692

## **Time-of-Flight Sensor**

v4-00 • 2021-Jul-08

## Abstract

The TMF8805 is a dToF (direct time of flight) optical distance sensor module achieving up to 2500mm target detection distance.

顶点光电子商城 https://www.vertex-icbuy.com/

## **Content Guide**

| 1                                                    | General Description 3                                                                                                                                  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.1<br>1.2<br>1.3                                    | Key Benefits & Features3<br>Applications4<br>Block Diagram4                                                                                            |  |

| 2                                                    | Ordering Information5                                                                                                                                  |  |

| 3                                                    | Pin Assignment 6                                                                                                                                       |  |

| 3.1<br>3.2                                           | Pin Diagram6<br>Pin Description6                                                                                                                       |  |

| 4                                                    | Absolute Maximum Ratings 8                                                                                                                             |  |

| 5                                                    | Electrical Characteristics9                                                                                                                            |  |

| 5.1                                                  | Recommended Operating Conditions9                                                                                                                      |  |

| 6                                                    | Typical Operating<br>Characteristics10                                                                                                                 |  |

| 7                                                    | Functional Description13                                                                                                                               |  |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8 | I²C Protocol.13System Parameters13I/O14Power Consumption15Timing16Algorithm Performance17VCSEL19Typical Optical Characteristics19                      |  |

| 8                                                    | Register Description21                                                                                                                                 |  |

| 8.1<br>8.2<br>8.3<br>8.4                             | APPID Register (Address 0x00)21<br>APPREV_MAJOR Register (Address<br>0x01)21<br>APPREQID Register (Address 0x02)21<br>ENABLE Register (Address 0xE0)22 |  |

| 8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10 | INT_STATUS Register (Address 0xE1)<br>INT_ENAB Register (Address 0xE2)<br>ID Register (Address 0xE3)<br>REVID Register (Address 0xE4)<br>App0 Registers – appid=0xC0<br>Bootloader Registers – appid=0x80 | 23<br>23<br>24<br>24<br>24<br>52 |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 9                                       | Application Information                                                                                                                                                                                   | . 56                             |

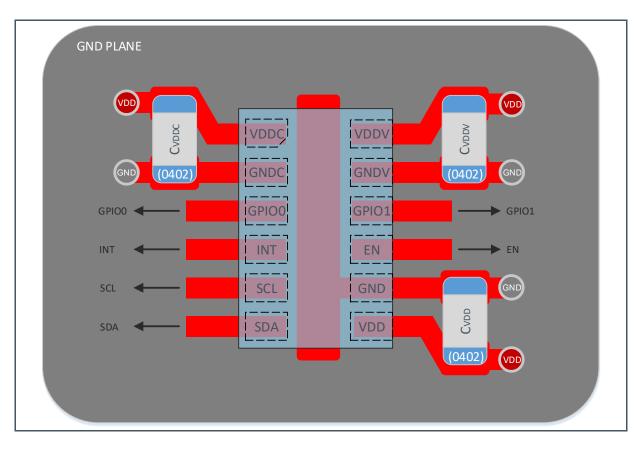

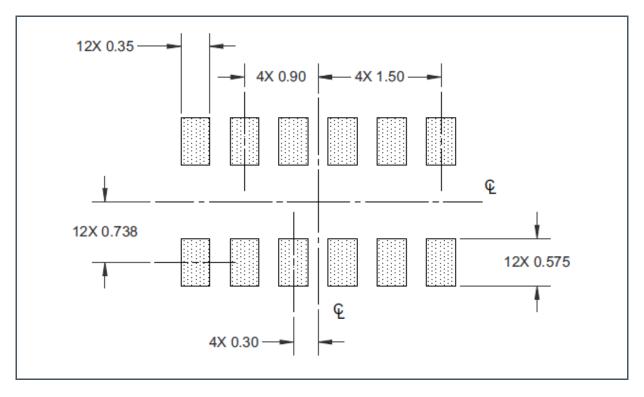

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5         | SPAD Options<br>Reference SPAD, TDC and Histogram<br>Schematic<br>PCB Layout<br>PCB Pad Layout                                                                                                            | 57<br>58<br>60                   |

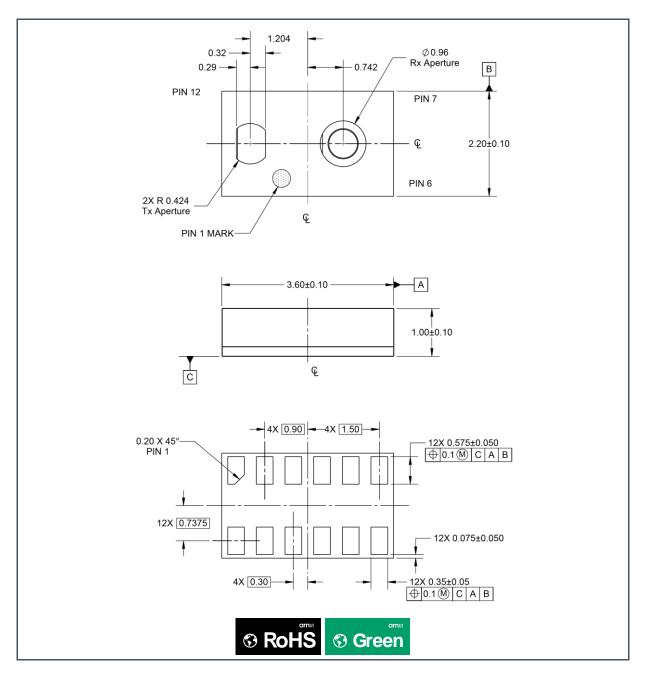

| 10                                      | Package Drawings & Markings                                                                                                                                                                               | . 62                             |

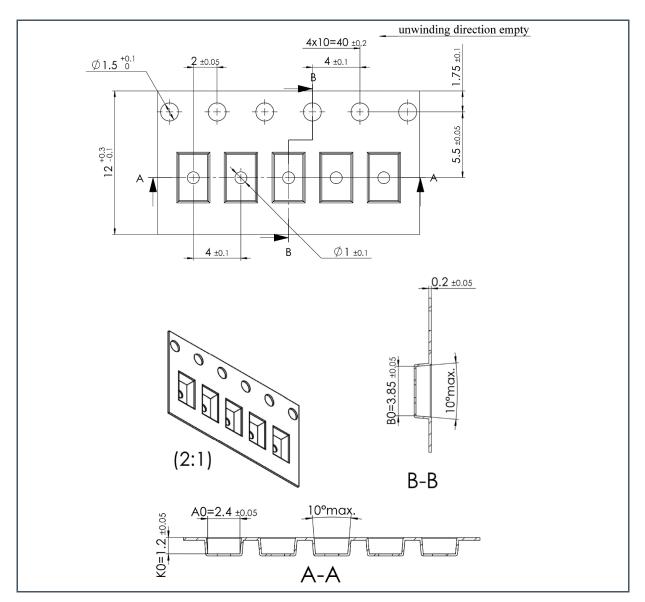

| 11                                      | Tape & Reel Information                                                                                                                                                                                   | . 63                             |

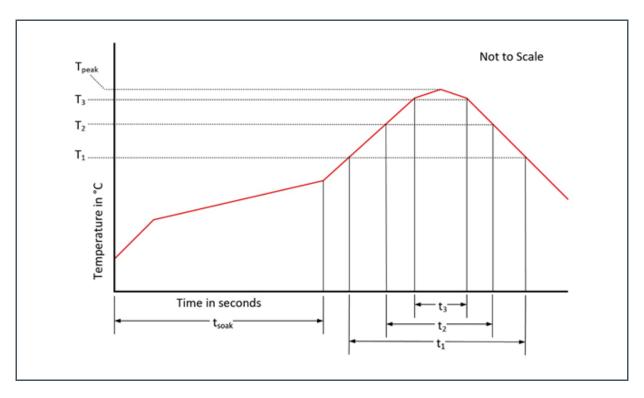

| 12                                      | Soldering & Storage Information                                                                                                                                                                           | <mark>ո 64</mark>                |

|                                         |                                                                                                                                                                                                           |                                  |

| 12.1<br>12.2                            | Soldering Information<br>Storage Information                                                                                                                                                              |                                  |

|                                         |                                                                                                                                                                                                           | 65                               |

| 12.2                                    | Storage Information                                                                                                                                                                                       | 65<br>. <b>.67</b>               |

## **1 General Description**

The TMF8805 is a time-of-flight (TOF) sensor in a single modular package with associated VCSEL. The TOF device is based on SPAD, TDC and histogram technology. The device achieves 2500 mm detection range.

### 1.1 Key Benefits & Features

The benefits and features of TMF8805, Time-of-Flight Sensor, are listed below:

Figure 1: Added Value of Using TMF8805

| Benefits                                                                                                 | Features                                                                                    |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Small footprint fits in the mobile phone bezel                                                           | Modular package - 2.2 mm x 3.6 mm x 1.0 mm                                                  |

| Detecting central closest objects                                                                        | No influence on multi object reflections                                                    |

| Within 5 % of measurement (accuracy); no multipath and no multiple object problems as for iToF           | Time-to-Digital Converter (TDC)<br>Direct Time-of-Flight Measurement                        |

| Better accuracy detects reliably closest<br>object<br>Minimum distance 20 mm<br>Maximum distance 2500 mm | Single Photon Avalanche Photodiode (SPAD)<br>Histogram based architecture                   |

| No complex calibration                                                                                   | Dynamic cover glass calibration                                                             |

| Compensates for dirt on glass                                                                            | Reliable Operation under demanding use cases                                                |

| Improved accuracy over temperature and life                                                              | Reference SPAD                                                                              |

| Make better decisions                                                                                    | Distance and signal quality reported                                                        |

| Class 1 Eye Safe                                                                                         | Fast VCSEL driver with protection                                                           |

| Longer battery life                                                                                      | 27 mA power consumption at 30 Hz operation<br>0.26 μA power-down current consumption (EN=0) |

## 1.2 Applications

The device is ideal for use in the mobile phone market with applications including:

- Distance measurement for camera autofocus (Laser Detect Autofocus LDAF)

- Supporting low-power system operation by enabling high-power components (i.e. 3D camera) only when an object is in the detection range

- Presence detection Object detection

- Collision avoidance

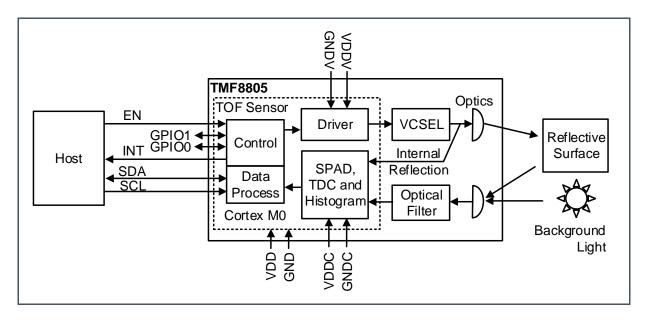

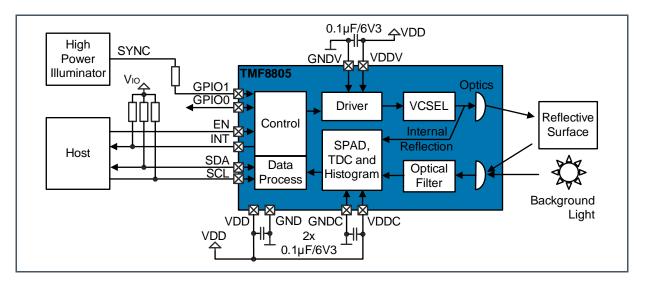

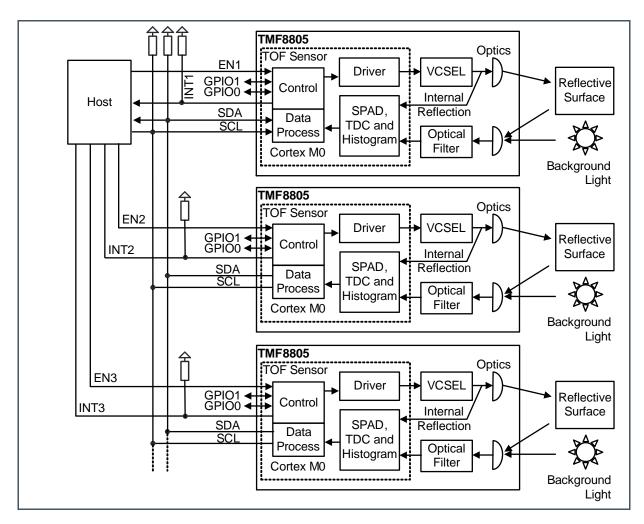

### 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2: Functional Blocks of TMF8805

## 2 Ordering Information

| Ordering Code | Package           | Marking                      | Delivery Form              | Delivery Quantity |

|---------------|-------------------|------------------------------|----------------------------|-------------------|

| TMF8805-1BM   | Optical<br>Module | 5-digit tracecode<br>(coded) | Tape & Reel<br>(7" reels)  | 500 pcs/reel      |

| TMF8805-1B    | Optical<br>Module | 5-digit tracecode<br>(coded) | Tape & Reel<br>(13" reels) | 5000 pcs/reel     |

## 3 Pin Assignment

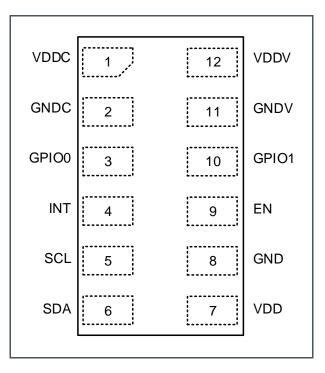

### 3.1 Pin Diagram

Figure 3:

Pin Locations Top Through View (not to scale)

## 3.2 Pin Description

#### Figure 4:

Pin Description of TMF8805

| Pin Number | Pin Name | Signal Type | Description                                                                                              |

|------------|----------|-------------|----------------------------------------------------------------------------------------------------------|

| 1          | VDDC     | Supply      | Charge pump supply voltage (3 V); add a<br>capacitor GRM155R70J104KA01 (0402 X7R<br>0.1 μF 6.3 V) to GND |

| 2          | GNDC     | Ground      | Charge pump ground; connect all ground pins together                                                     |

| 3          | GPIO0    | I/O         | General purpose input/output; default output low; leave open if not used                                 |

| Pin Number | Pin Name | Signal Type | Description                                                                                                                               |

|------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 4          | INT      | Output      | Interrupt. Open-drain output; connect to GND if not used                                                                                  |

| 5          | SCL      | Input       | I <sup>2</sup> C Serial Clock                                                                                                             |

| 6          | SDA      | I/O         | I <sup>2</sup> C Serial Data                                                                                                              |

| 7          | VDD      | Supply      | Chip Supply voltage (3 V); add a capacitor<br>GRM155R70J104KA01 (0402 X7R 0.1 µF<br>6.3 V) to GND                                         |

| 8          | GND      | Ground      | Chip Ground; connect all ground pins together                                                                                             |

| 9          | EN       | Input       | Enable input active high; setting to low forces<br>the device into shutdown and all memory<br>content is lost; connect to VDD if not used |

| 10         | GPIO1    | I/O         | General purpose input/output; default output low; leave open if not used                                                                  |

| 11         | GNDV     | Ground      | VCSEL Ground; connect all ground pins together                                                                                            |

| 12         | VDDV     | Supply      | VCSEL Supply voltage (3 V); add a capacitor GRM155R70J104KA01 (0402 X7R 0.1 $\mu F$ 6.3 V) to GND                                         |

(1) SDA, SCL, INT and EN have no diode to any VDD supply. Therefore even with VDD=0 V they do not block the interrupt line or I<sup>2</sup>C bus.

(2) GPIO0 and GPIO1 are push/pull output and have a diode to VDD; therefore if VDD is not powered, GPIO0 and GPIO1 should not be driven from outside.

## 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 5

Absolute Maximum Ratings of TMF8805

| Symbol               | Parameter                              | Min  | Max                          | Unit | Comments                                                                                     |

|----------------------|----------------------------------------|------|------------------------------|------|----------------------------------------------------------------------------------------------|

| Electrical Par       | ameters                                |      |                              |      |                                                                                              |

| VDDC,<br>VDDV, VDD   | 3 V Supply voltage                     | -0.3 | 3.6                          | V    | Connect pins VDDC,<br>VDDV, VDD on PCB with<br>very short connections                        |

| GNDV,<br>GNDC, GND   | Ground                                 | 0.0  | 0.0                          | V    | Connect all GND pins on<br>PCB with very short<br>connections                                |

| GPIO0,<br>GPIO1      | Digital I/O terminal voltage           | -0.3 | VDD +<br>0.3 V max.<br>3.6 V | V    | Protection diode to VDD                                                                      |

| INT, SCL,<br>SDA, EN | Digital I/O terminal voltage           | -0.3 | 3.6                          | V    | No protection diodes to<br>any positive supply only<br>to ground                             |

| I_SCR                | Latch up immunity                      | ±    | 100                          | mA   | JEDEC JESD78E                                                                                |

| Electrostatic        | Discharge                              |      |                              |      |                                                                                              |

| ESD <sub>HBM</sub>   | Electrostatic Discharge HBM            | ±    | 2000                         | V    | JEDEC JS-001-2017                                                                            |

| ESD <sub>CDM</sub>   | Electrostatic Discharge CDM            | ±    | 500                          | V    | JEDEC JS-002-2018                                                                            |

| Temperature          | Ranges and Storage Conditions          |      |                              |      |                                                                                              |

| T <sub>STRG</sub>    | Storage Temperature Range              | -40  | 85                           | °C   |                                                                                              |

| T <sub>BODY</sub>    | Package Body Temperature               |      | 260                          | °C   | IPC/JEDEC J-STD-020 <sup>(1)</sup>                                                           |

| RH <sub>NC</sub>     | Relative Humidity (non-<br>condensing) |      | 85                           | %    |                                                                                              |

| MSL                  | Moisture Sensitivity Level             |      | 3                            |      | Represents a maximum<br>floor life time of 168h with<br>$T_{AMB}$ < 30 °C and < 60 %<br>r.h. |

(1) The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices."

## **5** Electrical Characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

## 5.1 Recommended Operating Conditions

Device parameters are guaranteed at nominal conditions unless otherwise noted. While the device is operational across the temperature range, functionality will vary with temperature.

Figure 6:

**Recommended Operating Conditions of TMF8805**

| Symbol            | Parameter            | Min | Тур | Max | Unit | Comment     |

|-------------------|----------------------|-----|-----|-----|------|-------------|

| VDDV, VDDC, VDD   | 3 V supply voltage   | 2.7 | 3   | 3.3 | V    |             |

| Temperature Range | Free-air temperature | -30 | 25  | 70  | °C   | Operational |

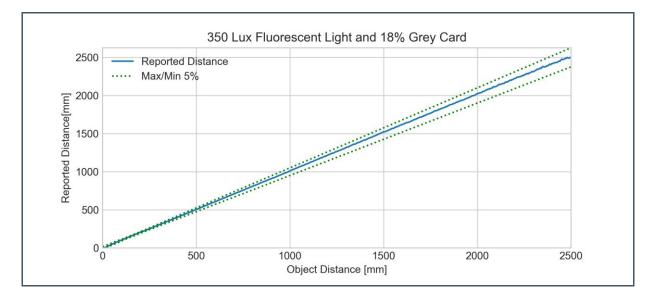

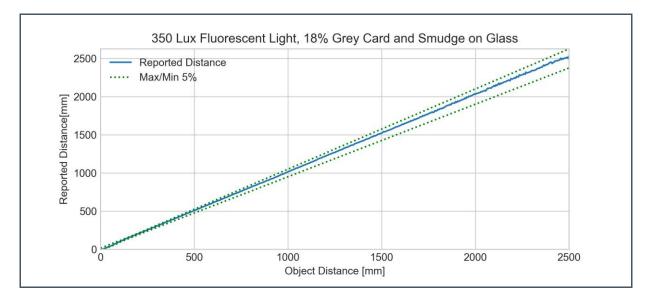

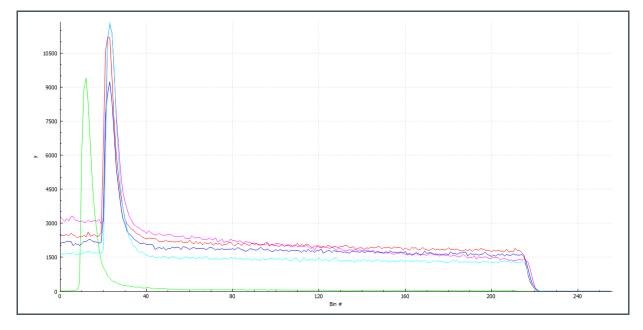

## **6** Typical Operating Characteristics

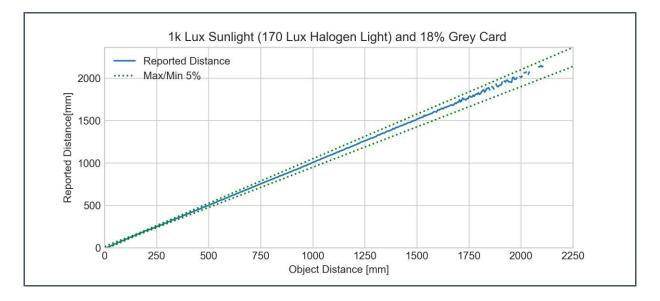

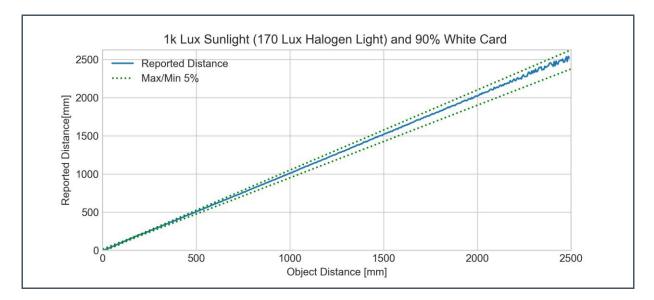

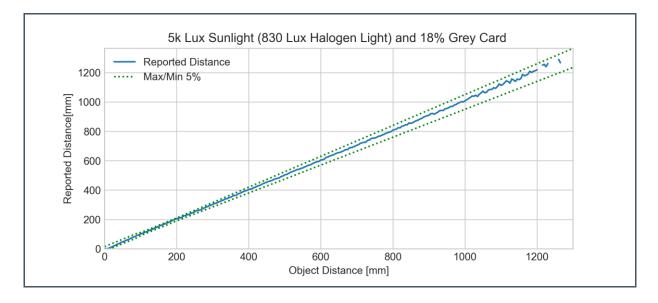

Following operating characteristics are measured with calibrated devices with full optical stack including glass and IR ink with >90 % transmissivity. The airgap is set to 0.38 mm. The ambient light is measured on the 1 m x 1 m target. A very diffuse scotch magic tape 810 is used for measurement with smudge.

#### Figure 7: 350 Lux Fluorescent Light and 18% Grey Card

#### Figure 9:

1 k Lux Sunlight Represented by 170 Lux Halogen Light and 18% Grey Card

Figure 10: 1 k Lux Sunlight Represented by 170 Lux Halogen Light and 90% White Card

#### Figure 11:

5 k Lux Sunlight Represented by 830 Lux Halogen Light and 18% Grey Card

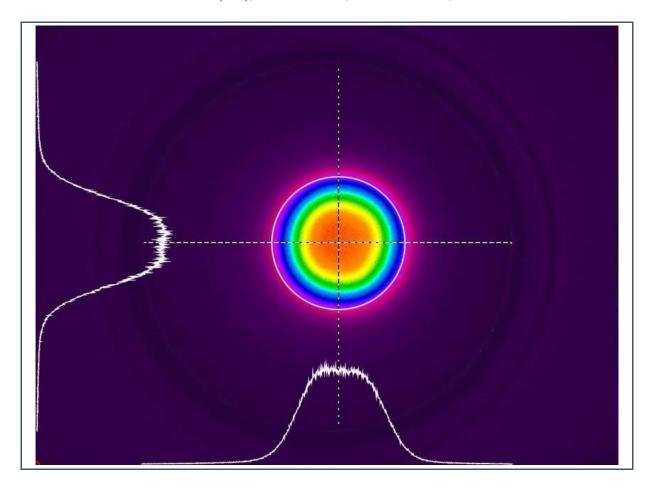

Figure 12: Field of Illumination of VCSEL (FOI), X-Axis: ±10.4°, Y-Axis: ±10.31°, 1/e<sup>2</sup>

## 7 Functional Description

### 7.1 I<sup>2</sup>C Protocol

The TMF8805 is controlled by an I<sup>2</sup>C bus, one interrupt pin and two GPIO pins.

The device uses I<sup>2</sup>C serial communication protocol for communication. The device supports 7-bit chip addressing and standard, fast mode and fast mode plus modes. Read and Write transactions comply with the standard set by Philips (now NXP). For a complete description of the I<sup>2</sup>C protocol, please review the NXP I<sup>2</sup>C design specification.

Internal to the device, an 8-bit buffer stores the register address location of the byte to read or write. This buffer auto-increments upon each byte transfer and is retained between transaction events (i.e. valid even after the master issues a STOP and the I<sup>2</sup>C bus is released). During consecutive Read transactions, the future/repeated I<sup>2</sup>C Read transaction may omit the memory address byte normally following the chip address byte; the buffer retains the last register address +1.

A Write transaction consists of a START, CHIP-ADDRESSWRITE, REGISTER-ADDRESSWRITE, DATA BYTE(S), and STOP. Following each byte (9TH clock pulse) the slave places an ACKNOWLEDGE/NOT- ACKNOWLEDGE (ACK/NACK) on the bus. If NACK is transmitted by the slave, the master may issue a STOP.

A Read transaction consists of a START, CHIP-ADDRESSWRITE, REGISTER-ADDRESS, RESTART, CHIP-ADDRESSREAD, DATA BYTE(S), and STOP. Following all but the final byte the master places an ACK on the bus (9TH clock pulse). Termination of the Read transaction is indicated by a NACK being placed on the bus by the master, followed by STOP.

The default I<sup>2</sup>C address is 0x41. The address can be changed after power-up. Use the enable pin to enable only one device at a time to provide unique device addresses.

## 7.2 System Parameters

The on-chip microprocessor is a Cortex M0 µP.

#### Figure 13:

**ARM M0 Parameters**

| Parameter              | Min | Nom   | Мах          | Units | Comment                                                                                                                                         |

|------------------------|-----|-------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| µP Operating Frequency |     | 4.7   | 75 (=4.7*16) | MHz   | The CPU can operate<br>with the RC oscillator<br>directly or with a 16x PLL;<br>frequency tuning adjusts<br>the default frequency to<br>4.7 MHz |

| RAM                    |     |       | 32           | kB    |                                                                                                                                                 |

| ROM                    |     |       | 32           | kB    |                                                                                                                                                 |

| Max PLL Frequency      |     | 150.4 |              | MHz   | for 4.7 MHz RC clock                                                                                                                            |

### 7.3 I/O

#### Figure 14:

**Typical I/O Level Specification**

| Symbol                 | Parameter                     | Condition                                               | Min  | Тур | Max  | Units |

|------------------------|-------------------------------|---------------------------------------------------------|------|-----|------|-------|

| ILEAK                  | SDA, SCL, GPIO0/1,<br>EN, INT |                                                         | -5   |     | 5    | μA    |

| VIH <sup>(1)</sup>     | SDA, SCL, GPIO0/1,<br>EN      |                                                         | 1.26 |     |      | V     |

|                        |                               | 2.7 V <vdd<2.9 v,<br="">&lt;400 kHz I²C speed</vdd<2.9> |      |     | 0.3  |       |

|                        | SDA, SCL                      | VDD >2.9 V,<br><400 kHz I²C speed                       |      |     | 0.54 | - V   |

| VIL_I2C <sup>(1)</sup> |                               | 2.8 V <vdd<3.0 v,<br="">&lt;1 MHz I²C speed</vdd<3.0>   |      |     | 0.3  | V     |

|                        |                               | VDD>3.0 V,<br><1 MHz I²C speed                          |      |     | 0.54 | -     |

| VIL                    | GPIO0/1, EN                   |                                                         |      |     | 0.54 | V     |

| VOL                    | SDA, GPIO0/1, INT             | 2 mA sink                                               | 0    |     | 0.36 | V     |

| VUL                    |                               | 4 mA sink                                               | 0    |     | 0.6  | V     |

| IDRIVE_H               | GPIO0/1                       | 1 V applied on GPIO                                     | 3.6  |     |      | mA    |

| IDRIVE_L               | GPIO0/1                       | 1 V applied on GPIO                                     | 3.9  |     |      | mA    |

(1) The input highlevel VIH and lowlevel VIL is defined to support a pullup supply of 1.8 V  $\pm$ 5 %

## 7.4 Power Consumption

All current consumption values include silicon process variation. Temperature and voltages are at nominal conditions (23 °C and 2.8 V).

Figure 15:

**Power Consumption**

| Parameter                                                                          | Condition                 | Min  | Nom  | Мах | Units | Comment                                  |

|------------------------------------------------------------------------------------|---------------------------|------|------|-----|-------|------------------------------------------|

| I_VDD Powerdown                                                                    | Enable Pin<br>Low I²C Off | 0.02 | 0.26 | 1   | μA    | State:<br>Powerdown                      |

| I_VDD Standby CPU Off,<br>RAM On OSC Off, pon=0<br>I <sup>2</sup> C Wakeup Only    |                           |      | 85   |     | μA    | State:<br>Standby                        |

| I_VDD Wait CPU Off,<br>RAM On, OSC On 5 MHz<br>I²C On, Timer Wakeup                |                           |      | 140  |     | μA    | State:<br>Wait                           |

| I_VDD Ranging<br>Processing CPU Running<br>at 80 MHz No VCSEL,<br>No TDC           |                           |      | 2.7  |     | mA    | State:<br>Histogram<br>processing        |

| I_VDD Ranging Active<br>CPU stopped<br>VCSEL_clk_div2=0<br>(default), TDCs running |                           |      | 32.5 |     | mA    | State:<br>Ranging active                 |

| I_VDD Ranging Active<br>CPU stopped<br>VCSEL_clk_div2=1,<br>TDCs running           |                           |      | 25.2 |     | mA    | State:<br>Ranging active                 |

| I_VDD Ranging 30 Hz, 33 ms, default settings                                       |                           |      | 27   |     | mA    | Average power consumption <sup>(1)</sup> |

| Peak VCSEL Current                                                                 |                           |      | 230  |     | mA    |                                          |

| Max VCSEL Duty Cycle                                                               |                           |      | 2    |     | %     |                                          |

(1) Current is reduced to typ. 17.7 mA if iteration is set to 600 k instead of 900 k and output data rate is maintained at 30 Hz by setting repetition\_period = 33 [ms]

## 7.5 Timing

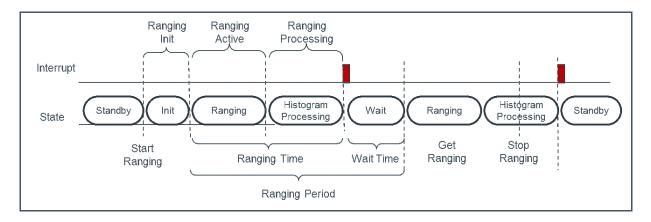

### 7.5.1 Ranging Acquisition Timing

Figure 16:

**Ranging Acquisition Timing**

| Parameter                                       | Min | Nom | Max | Units | Comment                                                                     |

|-------------------------------------------------|-----|-----|-----|-------|-----------------------------------------------------------------------------|

| Ranging Time Default Settings                   |     | 33  |     | ms    | Varies with operational mode                                                |

| Ranging Init (including electrical calibration) |     | 8   |     | ms    | Only done on startup and<br>if temperature changed<br>from last calibration |

| Ranging Period                                  |     |     | 209 | ms    | Programmable by the interface                                               |

Figure 17: Ranging Timing Diagram

### 7.5.2 Reset Pin and Power-Up Timing

Figure 18: Reset Pin and Power-Up Timing

| Parameter                            | Min | Nom | Max | Units | Comment                               |

|--------------------------------------|-----|-----|-----|-------|---------------------------------------|

| Power On (Boot Time)                 |     | 3   |     | ms    | Does not include<br>RAM download time |

| Enable high to ready for measurement |     | 8   |     | ms    |                                       |

| Parameter                     | Min | Nom | Max | Units | Comment |

|-------------------------------|-----|-----|-----|-------|---------|

| Standby to Active Time        |     | <<1 |     | ms    |         |

| Active to Standby Time        |     | <<1 |     | ms    |         |

| Enable Low to Power Down Time |     | <<1 |     | ms    |         |

## 7.6 Algorithm Performance

As the performance of the algorithm is dependent on the ROM version, following section only applies for devices with order code TMF8805-1B (and TMF8805-1BM), calibrated and in-application oscillator calibration using the reference driver code and patched with the latest software patch from ams – contact ams to identify latest patch version.

To achieve the full distance of 250 cm, the on chip oscillator needs to be tuned to 4.7 MHz.

The TMF8805 is embedded in the application using a 0.38 mm airgap and a glass with an IR ink with >90 % transmissivity. The glass thickness is 0.5 mm. An additional mask on the opaque ink is implemented according to TMF8805 optical design guide (external document).

#### 7.6.1 Calibration

To achieve the performance described in the next sections, a calibration of the algorithm needs to be performed (command = 0x0A). The TMF8805 shall be embedded in the final application and the cover glass including the IR ink needs to be assembled. The calibration test shall be done in a housing with minimal ambient light and no target within 40 cm in field of view of the TMF8805.

The TMF8805 generates a calibration data set which is permanently stored on the host.

On each power-up of the TMF8805 the calibration data set is sent by I<sup>2</sup>C to the TMF8805 prior to execution of any algorithms (commands=0x02 or 0x0B).

### 7.6.2 Algorithm Timings

The TMF8805 can adjust the number of iterations and detection threshold using registers. A default mode is defined having 900 k iterations and threshold=0.

### Figure 19:

Algorithm Timings

| Parameter    | Condition                                                               | Min | Nom | Мах | Units |

|--------------|-------------------------------------------------------------------------|-----|-----|-----|-------|

|              | command=0x02 or 0x03<br>cmd_data6=0xA3,                                 | 22  |     |     |       |

| Default mode | cmd_data3=0x00,<br>cmd_data1=0x03,<br>cmd_data0=0x84 (900 k iterations) |     | 33  |     | ms    |

#### 7.6.3 Algorithm Performance Parameters

The algorithm reports distance information of the closest object in 1 mm steps.

Using the timings described in 7.6.2 following performance is achieved:

Figure 20:

#### **Object Detection Algorithm Parameters**

| Parameter                                                       | Condition                                                                                         | Min | Nom                 | Max | Units |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|---------------------|-----|-------|

| Reflectivity of object at 940 nm                                | Perpendicular to TMF8805                                                                          | 18  |                     | 90  | %     |

|                                                                 | 350 lux fluorescent on object, 18% grey or 90% white card                                         |     | 2500(1)             |     | mm    |

|                                                                 | 170 lux halogen light on object <sup>(2)</sup> , 90% white card                                   |     | 2400 <sup>(1)</sup> |     | mm    |

| Maximum distance<br>detection, 1.5 m x<br>1.5 m object          | 170 lux halogen light on object <sup>(2)</sup> , 18% grey card                                    |     | 1900                |     | mm    |

|                                                                 | 170 lux halogen light on object <sup>(2)</sup> ,<br>18% grey card, smudge on glass <sup>(3)</sup> |     | 1500                |     | mm    |

|                                                                 | 830 lux halogen light on object <sup>(4)</sup> , 18% grey card                                    |     | 1100                |     | mm    |

| Minimum distance<br>detection, 18 % grey<br>card, 20 cm x 26 cm |                                                                                                   |     | 20                  |     | mm    |

|                                                                 | Object distance ≥ 200 mm                                                                          |     | ±5                  |     | %     |

| Accuracy                                                        | 100 mm ≤ object distance <200 mm                                                                  |     | ±10                 |     | mm    |

|                                                                 | 20 mm ≤ object distance <100 mm                                                                   |     | ±15                 |     | mm    |

| Transition short to long distance mode                          |                                                                                                   |     | 200                 |     | mm    |

- (1) To achieve the full distance, the oscillator need to be tuned to 4.7 MHz. Use **ams** reference code to implement clock frequency tuning.

- Any target reported above 2500 mm should be considered as no object.

- (2) 170 lux halogen light represents 1k lux sunlight equivalent; light on object only.

- (3) Smudge on glass is defined by one layer of Scotch Magic Tape 810 (very diffuse)

- (4) 830 lux halogen light represents 5 k lux sunlight equivalent; light on object only

### 7.7 VCSEL

Internal protection ensures no single point of failure will cause the VCSEL to violate the Class 1 Laser Safety.

Class 1

24°

Laser Safety

VCSEL Pulse Rep Rate

26.6 ns (37.6 MHz) If VCSEL\_clk\_div=1, the frequency is divided by two.

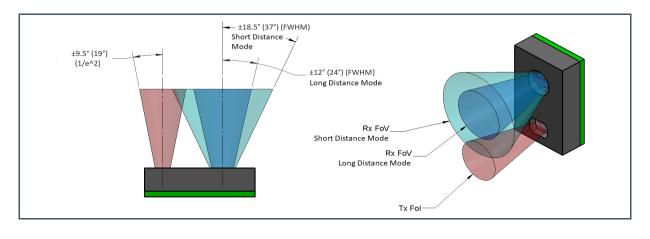

### 7.8 Typical Optical Characteristics

- VCSEL Field of Illumination (FOI) 25° 21°

- TOF Sensor Field of View (FOV) 37° F

- Full width from 1% of maximum up to maximum Full width from 5% of maximum up to maximum 1/e^2 FWHM – for short distances FWHM – for long distances

The SPAD FoV angular response uses the full TMF8805 SPADs for short distances. The SPAD FoV is reduced when the TMF8805 operates in long distance since the SPAD array is reduced. This helps to improve ambient light tolerance.<sup>1</sup>

Figure 21: FOI/FOV of TMF8805 (used 1/e<sup>2</sup> for FOI as example)

<sup>1</sup> It depends on the size and reflectivity of the object if TMF8805 algorithm detects off-axis objects.

#### 7.8.1 Filter Characteristics:

• FWHM

- 114 nm

- Passband Center Frequency

- 940 nm

- Stopband Wavelengths

- 350 nm 883 nm, 997 nm 1100 nm

## 8 **Register Description**

## 8.1 APPID Register (Address 0x00)

Figure 22: APPID Register

| Addr: 0x00 |       | APPID |      |                                                                                                          |

|------------|-------|-------|------|----------------------------------------------------------------------------------------------------------|

| Field      | Name  | Rst   | Туре | Description                                                                                              |

| 7:0        | appid | 0     | RW   | Currently running application:<br>0xC0 App0 – Measurement application running<br>0x80 bootloader running |

## 8.2 APPREV\_MAJOR Register (Address 0x01)

Figure 23: APPREV\_MAJOR Register

| Addr: 0x01 |             |     | APPREV | _MAJOR                     |

|------------|-------------|-----|--------|----------------------------|

| Field      | Name        | Rst | Туре   | Description                |

| 7:0        | apprevMajor | 0   | RW     | Application major revision |

## 8.3 APPREQID Register (Address 0x02)

### Figure 24:

**APPREQID** Register

| Addr : ( | Addr : 0x02 |     | APPREC | סוג                                                                                                                                                                            |

|----------|-------------|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field    | Name        | Rst | Туре   | Description                                                                                                                                                                    |

| 7:0      | appReqid    | 0   | RW     | Application that shall be started, set this to<br>0x80 bootloader<br>0xC0 App0 – measurement application<br>and wait until register 0x00 (APPID) shows this<br>as application. |

## 8.4 ENABLE Register (Address 0xE0)

### Figure 25:

ENABLE Register

| Addr: ( | Addr: 0xE0 |     | ENABLE | ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------|------------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field   | Name       | Rst | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 7       | cpu_reset  | 0   | RW_SC  | Write a '1' here to reset CPU. This generates global reset, fully resetting CPU and all CPU registers. The bit resets itself, no need to explicitly clear it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 6       | cpu_ready  | 0   | RO     | CPU is ready to handle I <sup>2</sup> C - if this bit is zero, then only<br>the registers 0xe0 and above are usable, the memory<br>mapped I <sup>2</sup> C space is not used.<br>Bit gets set only explicitly by software, therefore a<br>functional and running firmware is necessary for this bit<br>to work.                                                                                                                                                                                                                                                                                                                                                               |  |

| 0       | pon        | 1   | R_PUSH | <ul> <li>1=activate oscillator 0=ask cpu to go to standby</li> <li>Activating the oscillator is implemented in hardware.</li> <li>Whenever this register is '0' and a '1' is being written, the oscillator is being started and CPU receives a</li> <li>PON1 interrupt. It is implemented in the bootloader to execute a reset at this point, but the application goes to an IDLE state.</li> <li>De-activating the oscillator is a software assisted process. It is implemented in firmware. So writing a '0' to this register will trigger an internal CPU interrupt.</li> <li>The firmware, after powering down everything, sets the device into standby state.</li> </ul> |  |

## 8.5 INT\_STATUS Register (Address 0xE1)

#### Figure 26:

INT\_STATUS Register

| Addr: 0xE1 |                  | INT_STATU                                                                                                                                                    | INT_STATUS                                                                                                        |             |  |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------|--|

| Field      | Name             | Rst                                                                                                                                                          | Туре                                                                                                              | Description |  |

|            | 1 int2 0 R_PUSH1 |                                                                                                                                                              | Raw histogram available interrupt for App0; asserted when a raw histogram can be retrieved from I <sup>2</sup> C. |             |  |

| 1          |                  | int2 status. If bis is asserted, and int2_enab is asserted<br>as well, then the INT pin will be pulled low. Writing a '1'<br>here will clear int1 condition. |                                                                                                                   |             |  |

| Addr: 0xE1 |               | INT_STATU | INT_STATUS                                                                                                                                             |             |  |

|------------|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| Field      | Name          | Rst       | Туре                                                                                                                                                   | Description |  |

|            | 0 int1 0 R_PU |           | Object detection interrupt for App0; asserted when a result from object detection is available                                                         |             |  |

| 0          |               | R_PUSH1   | int1 status. If bis is asserted, and int1_enab is asserted as well, then the INT pin will be pulled low. Writing a '1' here will clear int1 condition. |             |  |

|            |               |           | Note: An interrupt is raised on every result from object detection including no-target.                                                                |             |  |

## 8.6 INT\_ENAB Register (Address 0xE2)

Figure 27: INT\_ENAB Register

| Addr: 0xE2    |      | INT_EN                  | INT_ENAB                                                                                                                                                                                     |  |  |

|---------------|------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name          | Rst  | Туре                    | Description                                                                                                                                                                                  |  |  |

| int2_enab     | 0    | RW                      | Raw histogram available interrupt for App0; asserted<br>when a raw histogram can be retrieved from I <sup>2</sup> C.<br>0=disabled, 1=enabled -> INT output is active if int2<br>flag is "1" |  |  |

|               |      |                         | Object detection interrupt for App0; asserted when a result from object detection is available                                                                                               |  |  |

| 0 int1_enab 0 | 0    | RW                      | 0=disabled, 1=enabled -> INT output is active if int1<br>flag is "1"                                                                                                                         |  |  |

|               | Name | Name Rst<br>int2_enab 0 | NameRstTypeint2_enab0RW                                                                                                                                                                      |  |  |

## 8.7 ID Register (Address 0xE3)

Figure 28: ID Register

| Addr: 0xE3 |      | ID  |      |                                                                             |

|------------|------|-----|------|-----------------------------------------------------------------------------|

| Field      | Name | Rst | Туре | Description                                                                 |

| 5:0        | id   | 0   | RO   | Chip ID, reads 07h – do not rely on register bits 6 and 7 of this register. |

## 8.8 REVID Register (Address 0xE4)

Figure 29:

**REVID Register**

| Addr: 0xE4 |        | REVID |      |                  |

|------------|--------|-------|------|------------------|

| Field      | Name   | Rst   | Туре | Description      |

| 2:0        | rev_id | 0     | RO   | Chip revision ID |

## 8.9 App0 Registers – appid=0xC0

Following registers are only available if appid=0xC0 (App0):

#### 8.9.1 CMD\_DATA9 Register (Address 0x06)

Figure 30: CMD\_DATA9 Register

| Addr: 0x06 |           |     | CMD_DA | CMD_DATA9                                                                                 |  |

|------------|-----------|-----|--------|-------------------------------------------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                                                               |  |

| 7:0        | cmd_data9 | 0   | W      | Command data 9 – see COMMAND Register<br>(Address 0x10); for future extension of commands |  |

### 8.9.2 CMD\_DATA8 Register (Address 0x07)

Figure 31: CMD\_DATA8 Register

| Addr: 0x07 |           |     | CMD_D/ | CMD_DATA8                                                                              |  |

|------------|-----------|-----|--------|----------------------------------------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                                                            |  |

| 7:0        | cmd_data8 | 0   | W      | Command data 8 – see COMMAND Register (Address 0x10); for future extension of commands |  |

### 8.9.3 CMD\_DATA7 Register (Address 0x08)

Figure 32:

CMD\_DATA7 Register

| Addr: 0x08 |           |     | CMD_DA | CMD_DATA7                                               |  |

|------------|-----------|-----|--------|---------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                             |  |

| 7:0        | cmd_data7 | 0   | W      | Command data 7 – see COMMAND Register<br>(Address 0x10) |  |

#### 8.9.4 CMD\_DATA6 Register (Address 0x09)

Figure 33:

CMD\_DATA6 Register

| Addr: 0x09 |           |     | CMD_DA | CMD_DATA6                                               |  |

|------------|-----------|-----|--------|---------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                             |  |

| 7:0        | cmd_data6 | 0   | W      | Command data 6 – see COMMAND Register<br>(Address 0x10) |  |

### 8.9.5 CMD\_DATA5 Register (Address 0x0A)

Figure 34: CMD\_DATA5 Register

| Addr: 0x0A |           |     | CMD_DATA5 |                                                         |

|------------|-----------|-----|-----------|---------------------------------------------------------|

| Field      | Name      | Rst | Туре      | Description                                             |

| 7:0        | cmd_data5 | 0   | W         | Command data 5 – see COMMAND Register<br>(Address 0x10) |

### 8.9.6 CMD\_DATA4 Register (Address 0x0B)

Figure 35:

CMD\_DATA4 Register

| Addr: 0x0B |           |     | CMD_D | CMD_DATA4                                            |  |  |

|------------|-----------|-----|-------|------------------------------------------------------|--|--|

| Field      | Name      | Rst | Туре  | Description                                          |  |  |

| 7:0        | cmd_data4 | 0   | W     | Command data 4 – see COMMAND Register (Address 0x10) |  |  |

#### 8.9.7 CMD\_DATA3 Register (Address 0x0C)

Figure 36:

CMD\_DATA3 Register

| Addr: 0x0C |           |     | CMD_DA | CMD_DATA3                                               |  |

|------------|-----------|-----|--------|---------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                             |  |

| 7:0        | cmd_data3 | 0   | W      | Command data 3 – see COMMAND Register<br>(Address 0x10) |  |

### 8.9.8 CMD\_DATA2 Register (Address 0x0D)

Figure 37: CMD\_DATA2 Register

| Addr: 0x0D |           |     | CMD_D | CMD_DATA2                                            |  |

|------------|-----------|-----|-------|------------------------------------------------------|--|

| Field      | Name      | Rst | Туре  | Description                                          |  |

| 7:0        | cmd_data2 | 0   | W     | Command data 2 – see COMMAND Register (Address 0x10) |  |

### 8.9.9 CMD\_DATA1 Register (Address 0x0E)

Figure 38:

CMD\_DATA1 Register

| Addr: 0x0E |           |     | CMD_DA | CMD_DATA1                                            |  |

|------------|-----------|-----|--------|------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                          |  |

| 7:0        | cmd_data1 | 0   | W      | Command data 1 – see COMMAND Register (Address 0x10) |  |

#### 8.9.10 CMD\_DATA0 Register (Address 0x0F)

Figure 39: CMD\_DATA0 Register

| Addr: 0x0F |           |     | CMD_D/ | CMD_DATA0                                            |  |

|------------|-----------|-----|--------|------------------------------------------------------|--|

| Field      | Name      | Rst | Туре   | Description                                          |  |

| 7:0        | cmd_data0 | 0   | W      | Command data 0 – see COMMAND Register (Address 0x10) |  |

### 8.9.11 COMMAND Register (Address 0x10)

Figure 40:

COMMAND Register

| Addr: ( | Addr: 0x10 |     | COMMAND |                                                                                |                                                                                       |                                                                                                                                                                                                                                                  |

|---------|------------|-----|---------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field   | Name       | Rst | Туре    | Descrip                                                                        | tion                                                                                  |                                                                                                                                                                                                                                                  |

| 7:0     | command    | 0   | RW      | Direct the device to control or select contents of the registers from 0x200xDF |                                                                                       | 8                                                                                                                                                                                                                                                |

|         |            |     |         | Setting                                                                        | Meaning                                                                               | ]                                                                                                                                                                                                                                                |

|         |            |     |         | 0x00                                                                           | No com                                                                                | mand                                                                                                                                                                                                                                             |

|         |            |     |         |                                                                                |                                                                                       | to perform target distance measurement with 8 bytes of data ng where including setting of calibration (and algorithm state) ation.                                                                                                               |

|         |            |     |         |                                                                                |                                                                                       | ata7 = Bit mask which calibration/state data was downloaded from to TMF8805 prior to setting this command:                                                                                                                                       |

|         |            |     |         |                                                                                | Bits                                                                                  | Definition                                                                                                                                                                                                                                       |

|         |            |     |         | 0x02                                                                           | 0                                                                                     | dataFactoryCal: When 1 data from register 0x20 onward includes factory calibration                                                                                                                                                               |

|         |            |     |         |                                                                                | 1                                                                                     | dataAlgState: If set, also set dataFactoryCal=1. Data from register 0x20 onwards includes factory calibration and algorithm state.                                                                                                               |

|         |            |     |         |                                                                                |                                                                                       | ata6 cmd_data0: Identical to command=0x03.                                                                                                                                                                                                       |

|         |            |     |         |                                                                                |                                                                                       | to perform target distance measurement with 7 bytes of data ng where                                                                                                                                                                             |

|         |            |     |         |                                                                                | cmd_da                                                                                | ata6 = Bit mask which algorithm is used                                                                                                                                                                                                          |

|         |            |     |         |                                                                                | Bits                                                                                  | Definition                                                                                                                                                                                                                                       |

|         |            |     |         |                                                                                | 0                                                                                     | Set to '1'                                                                                                                                                                                                                                       |

|         |            |     |         |                                                                                | 1                                                                                     | Set to '1'                                                                                                                                                                                                                                       |

|         |            |     |         | 002                                                                            | 2                                                                                     | VCSEL_clk_div2: If set, operates the VCSEL clock at half frequency - see section 7.7 - and doubles the ranging active tim where the VCSEL is enabled. It is recommended to use together with spread_spectrum_mode=1.                             |

|         |            |     |         | 0x03                                                                           | 3                                                                                     | Reserved; set to 0b.                                                                                                                                                                                                                             |

|         |            |     |         |                                                                                | 4                                                                                     | algImmediateInterrupt – When 1 target distance measurement<br>will immediately report to the host an interrupt of the capturing<br>caused by a GPIO event; when 0, will only report to the host<br>when target distance measurement was finished |

|         |            |     |         | 5                                                                              | When 1 combine the capture of the short and long distance histogram for maximum speed |                                                                                                                                                                                                                                                  |

|         |            |     |         |                                                                                | 6                                                                                     | Reserved; set to 0.                                                                                                                                                                                                                              |

|         |            |     |         |                                                                                | 7                                                                                     | When 1 do not go to standby between measurements (faster measurement times but higher current consumption)                                                                                                                                       |

#### cmd\_data5 = Bits for GPIO control

#### Bits Definition

- 3:0 GPIO0 settings

- 0 Input

1 - Input: active low disables collection, immediately abandoning current measurement. Returning to high restarts new measurement

2 - Input: active high disables collection, immediately abandoning current measurement. Returning to low restarts new measurement

- 3 Output: VCSEL pulse output see cmd\_data4

- 4 Output low (default after startup)

- 5 Output high

- 6:15 Reserved, do not use

- 7:4 GPIO1 settings

- 0 Input

1 - Input: active low disables collection, immediately abandoning current measurement. Returning to high restarts new measurement

2 - Input: active high disables collection, immediately

abandoning current measurement. Returning to low restarts new measurement

- 3 Output: VCSEL pulse output see cmd\_data4

- 4 Output low (default after startup)

- 5 Output high

- 6:15 Reserved, do not use

**cmd\_data4** = If cmd\_data5 enables VCSEL pulse output for GPIO0 and/or GPIO1, cmd\_data4 sets its timings as follows:

#### Value Meaning

- 0 No signal

- 1 GPIOx, rises 0 µs time before VCSEL pulse starts

- 2 GPIOx rises 100 µs before VCSEL pulse

- 3 GPIOx rises 200 µs before VCSEL pulse and so on

The falling edge of GPIOx happens at the same time the VCSEL stops emitting light.

cmd\_data3 = Object detection threshold and spread spectrum mode

#### Bits Definition

5:0 Object detection threshold – use 0 as default value

6 spread\_spectrum\_mode: If set, avoids aliasing of objects into measurement range. Use together with VCSEL\_clk\_div2=1 otherwise maximum distance is reduced and false objects at far distance can occur.

7 Set to '0'

**cmd\_data2** = repetition\_period in mSec, use 0 for single measurement; if the repetition period is set lower than the ranging time for this mode, the TMF8805 runs at it maximum possible speed (best effort approach).

cmd\_data1 = Number of iterations, low byte; 1 LSB=1 k

cmd\_data0 = Number of iterations, high byte; 1 LSB=1 k\*256

Once a measurement is finished, the interrupt is asserted if it is enabled by int1\_enab. Additionally the transaction ID tid is updated

| Addr: 0x10          |  |  | COMMAND |             |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------|--|--|---------|-------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Field Name Rst Type |  |  | Descrip | Description |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                     |  |  |         | 0x0A        | glass, r                      | n factory calibration in the final customer application including cover<br>no ambient light and no target.<br>sult from the factory calibration is stored from register 0x20 onwards                                                                                                                                                                                                                                                                                      |  |  |

|                     |  |  |         |             | (14 byte<br>Set flag<br>TMF88 | to download calibration (and algorithm state) configuration to                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                     |  |  |         |             | cmd_d                         | ata0 = Bit mask which calibration/state data was downloaded from                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                     |  |  |         |             | Bits                          | t to TMF8805 prior to setting this command:<br>Definition                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                     |  |  |         | 0x0B        | 0                             | dataFactoryCal: when 1 data from register 0x20 onward includes factory calibration                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|                     |  |  |         |             | 1                             | dataAlgState: if set, also set dataFactoryCal=1. Data from<br>register 0x20 onwards includes factory calibration and algorithm<br>state.                                                                                                                                                                                                                                                                                                                                  |  |  |

|                     |  |  |         |             | 0.                            | o control setting without actually performing a measurement as<br>nds 0x02 or 0x03 would do:                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                     |  |  |         |             | cmd_d                         | ata0 = Bits for GPIO control                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                     |  |  |         |             | Bits                          | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                     |  |  |         | 0x0F        | 3:0                           | <ul> <li>GPIO0 settings</li> <li>0 – Input</li> <li>1 - Input: active low disables collection, immediately abandoning current measurement. Returning to high restarts new measurement</li> <li>2 - Input: active high disables collection, immediately abandoning current measurement. Returning to low restarts new measurement</li> <li>3 - Output: VCSEL pulse output</li> <li>4 - Output low</li> <li>5 - Output high</li> <li>6:15 – Reserved, do not use</li> </ul> |  |  |

|                     |  |  |         |             | 7:4                           | <ul> <li>GPIO1 settings</li> <li>0 - Input</li> <li>1 - Input: active low disables collection, immediately abandoning current measurement. Returning to high restarts new measurement</li> <li>2 - Input: active high disables collection, immediately abandoning current measurement. Returning to low restarts new measurement</li> <li>3 - Output: VCSEL pulse output</li> <li>4 - Output low</li> <li>5 - Output high</li> <li>6:15 - Reserved, do not use</li> </ul> |  |  |

|                     |  |  |         |             | histogra<br>the sele          | histogram readout; the internal state machine will stop when a<br>am (e.g. calibration) is available and wait for readout by the host. If<br>ected histogram is readout, the host shall continue the state<br>e by sending command 0x32                                                                                                                                                                                                                                   |  |  |

|                     |  |  |         |             | cmd_d                         | ata3 = Bitmask for the histograms to be readout:                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                     |  |  |         | 0x30        | Bit                           | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                     |  |  |         |             | 0                             | Always set to '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                     |  |  |         |             | 1                             | Set to get electrical calibration histograms                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                     |  |  |         |             | 2                             | Set to get optical calibration histogram                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                     |  |  |         |             | 3                             | Always set to '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Addr: 0x10 |      |     | COMMAND |         |                                |                                                                                                                                                                                                                                               |  |

|------------|------|-----|---------|---------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field      | Name | Rst | Туре    | Descrip | tion                           |                                                                                                                                                                                                                                               |  |