# Product Document

Published by ams OSRAM Group

## Datasheet

DS001046

## **14-Channel Multi-Spectral Sensor**

v2-00 • 2022-Feb-10

顶点光电子商城 https://www.vertex-icbuy.com/

## **Content Guide**

| 1                               | General Description 3                                                                                                                                                    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3               | Key Benefits & Features3<br>Applications4<br>Block Diagram4                                                                                                              |

| 2                               | Ordering Information5                                                                                                                                                    |

| 3                               | Pin Assignment 6                                                                                                                                                         |

| 3.1<br>3.2                      | Pin Diagram6<br>Pin Description6                                                                                                                                         |

| 4                               | Absolute Maximum Ratings 8                                                                                                                                               |

| 5                               | Electrical Characteristics9                                                                                                                                              |

| 6                               | Optical Characteristics10                                                                                                                                                |

| 7                               | Typical Operating<br>Characteristics14                                                                                                                                   |

| 8                               | Functional Description15                                                                                                                                                 |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5 | Device Architecture         16           Sensor Array.         17           GPIO.         17           Interrupt (INT).         17           LED Driver (LDR)         17 |

| 9                               | I <sup>2</sup> C Interface18                                                                                                                                             |

| I <sup>2</sup> C Address<br>I <sup>2</sup> C Write Transaction<br>I <sup>2</sup> C Read Transaction<br>Timing Characteristics<br>Timing Diagrams | .19<br>.19<br>.19                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Description                                                                                                                             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Register Overview<br>Detailed Register Description                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

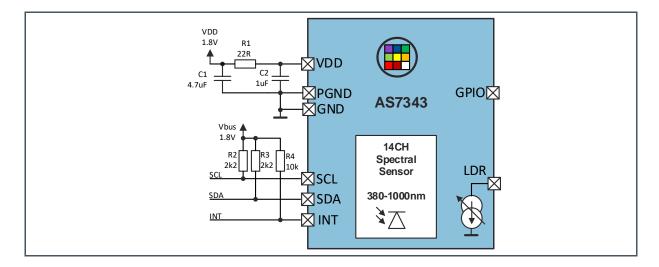

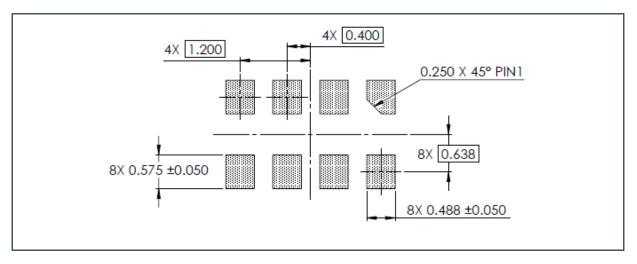

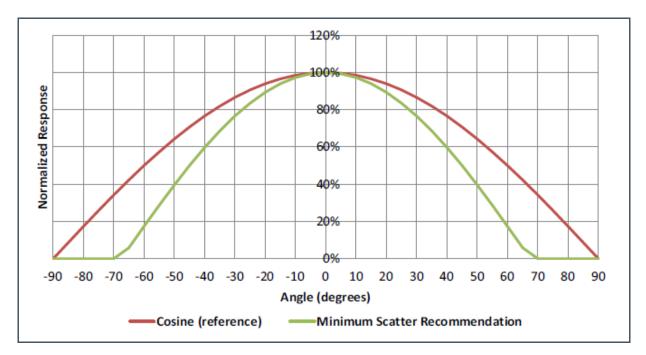

| Application Information                                                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Schematic<br>PCB Pad Layout<br>Application Optical Requirements                                                                                  | .49                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

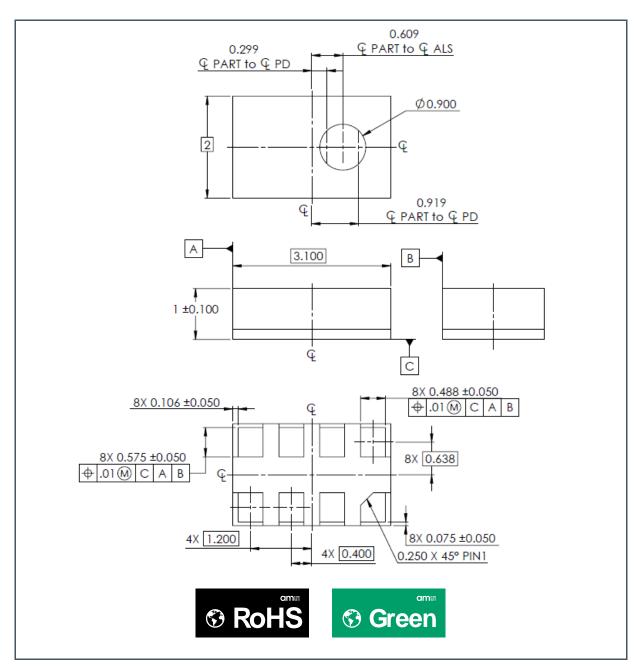

| Package Drawings & Markings                                                                                                                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

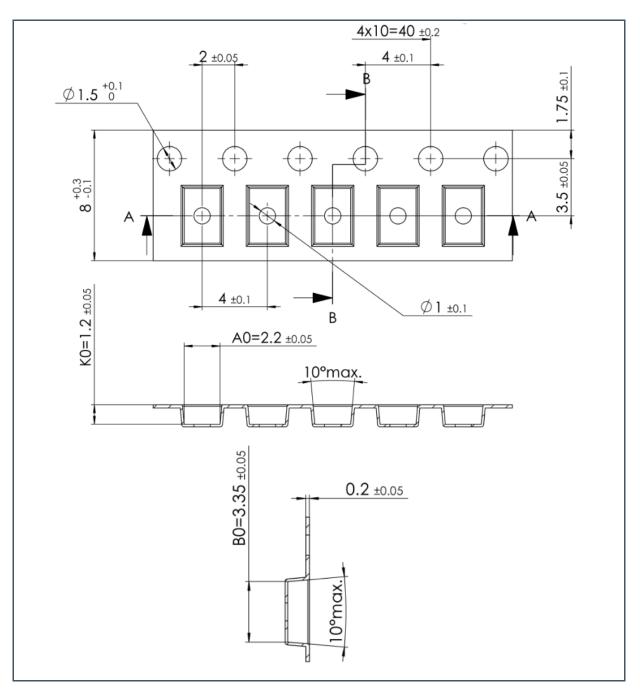

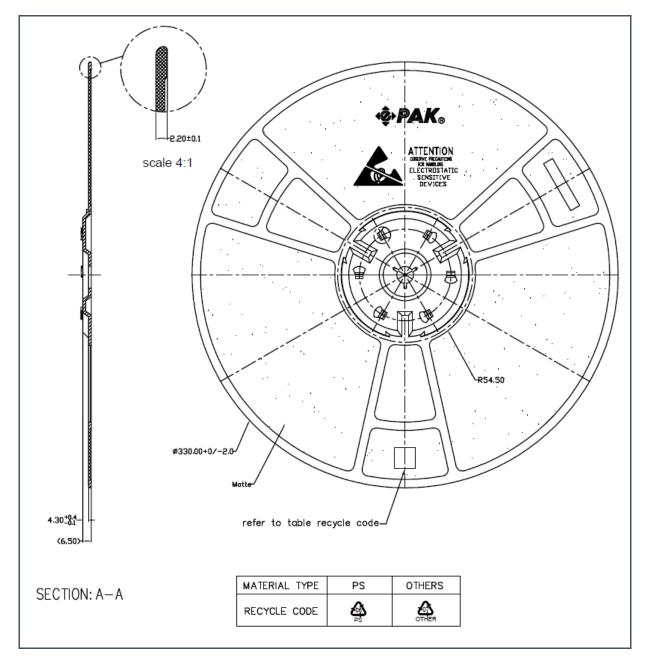

| Tape & Reel Information                                                                                                                          | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

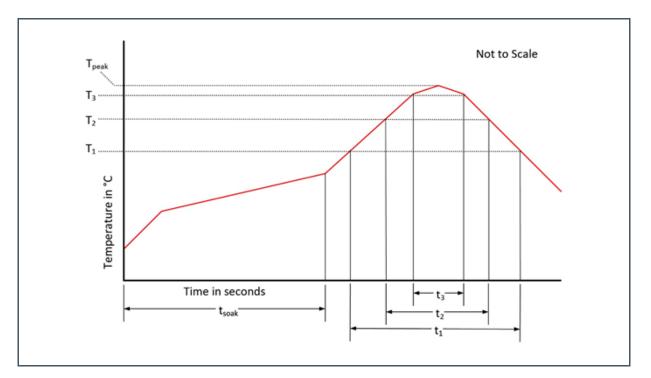

| Soldering & Storage Information                                                                                                                  | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Storage Information                                                                                                                              | .55                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Revision Information                                                                                                                             | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Legal Information                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                  | I <sup>2</sup> C Write Transaction<br>I <sup>2</sup> C Read Transaction<br>Timing Characteristics<br>Timing Diagrams<br><b>Register Description</b><br>Register Overview<br>Detailed Register Description<br><b>Application Information</b><br>Schematic<br>PCB Pad Layout<br>Application Optical Requirements<br><b>Package Drawings &amp; Markings</b><br><b>Tape &amp; Reel Information</b><br><b>Soldering &amp; Storage Information</b><br>Storage Information |

## **1** General Description

The **ams** AS7343 is a 14-channel highly versitile, multi-purpose spectral sensor enabling new consumer, commercial, industrial and laboratory applications. It is optimized for reflective, transmissive and emissive measurements including color matching, fluid or reagent analysis, lateral flow test applications and spectral identification in the visible range.

The spectral response is defined by individual channels covering approximately 380 nm to 1000 nm with 11 channels centered in the visible spectrum (VIS), plus one near-infrared (NIR) and a clear channel.

AS7343 integrates high-precision optical filters onto standard CMOS silicon via deposited interference filter technology. A built-in aperture controls the light entering the sensor array to increase accuracy. A programmable digital GPIO and LED driver enable light source and trigger/sync control. Device control and spectral data access is implemented through a serial I<sup>2</sup>C interface. The device is available in an ultra-low profile package with dimensions of 3.1 mm x 2 mm x 1 mm.

### 1.1 Key Benefits & Features

The benefits and features of AS7343, 14-Channel Multi-Spectral Sensor, are listed below:

### Figure 1:

Added Value of Using AS7343

| Benefits                                                   | Features                                                                                                                                                      |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Highly versatile multi-purpose spectral sensor             | <ul><li>14 channels between 380 nm and 1000 nm</li><li>Reflective, transmissive and emissive applications</li></ul>                                           |

| Highest sensitivity                                        | <ul> <li>Enables ultra-low light operation</li> <li>Enables operation behind dark glass or additional external filters</li> </ul>                             |

| Low power consumption and minimum I <sup>2</sup> C traffic | <ul><li>1.8 V VDD operation</li><li>Configurable sleep mode</li><li>Interrupt-driven device</li></ul>                                                         |

| Ultra-high integration                                     | <ul> <li>On chip interference filter technology</li> <li>Integrated LED driver and 6 integrated ADCs</li> <li>3.1 mm x 2 mm x 1 mm package outline</li> </ul> |

### 1.2 Applications

- Emissive light measurement

- Transmissive and reflective measurements such as fluid or color measurements

- Photoelectric smoke detectors

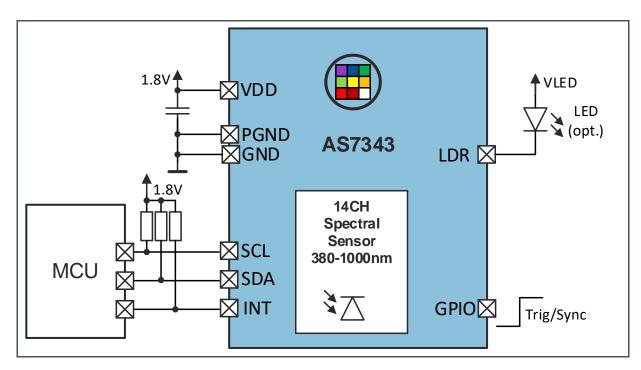

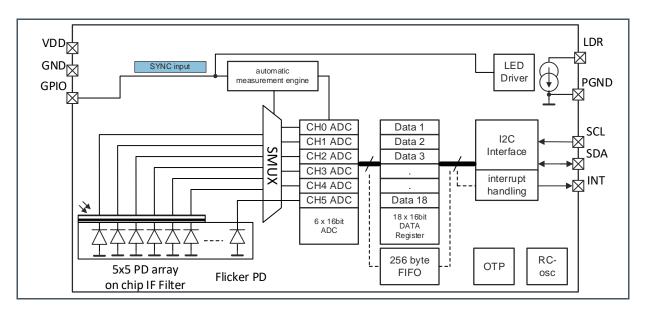

### 1.3 Block Diagram

The functional blocks of this device are shown below:

Figure 2 :

Functional Blocks of AS7343

## 2 Ordering Information

| Ordering Code | Package | Delivery Form       | Delivery Quantity | I2C Slave Address |

|---------------|---------|---------------------|-------------------|-------------------|

| AS7343-DLGT   | OLGA-8  | Tape & Reel 13-inch | 10000 pcs/reel    | 0x39              |

| AS7343-DLGM   | OLGA-8  | Tape & Reel 7-inch  | 500 pcs/reel      | 0x39              |

| AS7343B-DLGT  | OLGA-8  | Tape & Reel 13-inch | 10000 pcs/reel    | 0x29              |

## amu

## 3 Pin Assignment

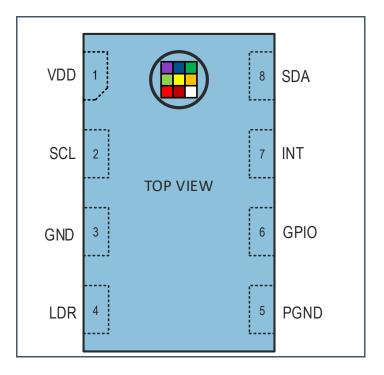

### 3.1 Pin Diagram

Figure 3:

Pin Assignment of AS7343 (TOP VIEW)

### 3.2 Pin Description

### Figure 4:

Pin Description of AS7343

| Pin Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                                              |

|------------|----------|-------------------------|----------------------------------------------------------------------------------------------------------|

| 1          | VDD      | Р                       | Positive supply voltage terminal                                                                         |

| 2          | SCL      | DI                      | Serial interface clock signal line for I <sup>2</sup> C interface.<br>Connect pull up resistor to 1.8 V. |

| 3          | GND      | Р                       | Ground. All voltages referenced to GND                                                                   |

| 4          | LDR      | A_I/O                   | LED current sink input. If not used leave pin unconnected.                                               |

| 5          | PGND     | Р                       | Ground. All voltages referenced to GND                                                                   |

| 6          | GPIO     | D_I/O                   | General purpose input/output. Default output open drain. If not used leave pin unconnected.              |

| Pin Number      | Pin Name          | Pin Type <sup>(1)</sup> | Description                                                                                                    |

|-----------------|-------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|

| 7               | INT               | DO_OD                   | Interrupt. Open drain output active low. Connect pull up resistor to 1.8 V. If not used leave pin unconnected. |

| 8               | SDA               | D_I/O                   | Serial interface data signal line for I <sup>2</sup> C interface.<br>Connect pull up resistor to 1.8 V.        |

| (1) Explanation | of abbreviations: |                         |                                                                                                                |

| Explanation | of abbreviations:          |

|-------------|----------------------------|

| DI          | Digital Input              |

| D_I/O       | Digital Input/Output       |

| DO_OD       | Digital Output, open drain |

| Р           | Power pin                  |

| A_I/O       | Analog pin                 |

|             |                            |

Datasheet • PUBLIC DS001046 • v2-00 • 2022-Feb-10

## amu

## 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. All voltages with respect to GND/PGND. Device parameters are guaranteed at V<sub>DD</sub>=1.8 V and T<sub>A</sub>=25 °C unless otherwise noted.

#### Figure 5:

**Absolute Maximum Ratings of AS7343**

| Symbol               | Parameter                              | Min  | Мах  | Unit | Comments                                    |

|----------------------|----------------------------------------|------|------|------|---------------------------------------------|

| Electrical Pa        | arameters                              |      |      |      |                                             |

| $V_{DD}$ / $V_{GND}$ | Supply Voltage to Ground               | -0.3 | 1.98 | V    | Applicable for pin VDD                      |

| V <sub>ANA_MAX</sub> | Analog Pins                            | -0.3 | 3.6  | V    | Applicable for pin LDR                      |

| V <sub>DIG_MAX</sub> | Digital Pins                           | -0.3 | 3.6  | V    | Applicable for pins<br>SCL,SDA,GPIO and INT |

| I <sub>SCR</sub>     | Input Current (latch-up immunity)      | ± ′  | 100  | mA   | AEC-Q100-004E                               |

| lo                   | Output Terminal Current                | -1   | 20   | mA   |                                             |

| Electrostatio        | c Discharge                            |      |      |      |                                             |

| ESD <sub>HBM</sub>   | Electrostatic Discharge HBM            | ± 2  | .000 | V    | JS-001-2017                                 |

| ESD <sub>CDM</sub>   | Electrostatic Discharge CDM            | ± {  | 500  | V    | JS-002-2018                                 |

| Temperature          | e Ranges and Storage Conditions        |      |      |      |                                             |

| T <sub>A</sub>       | Operating Ambient Temperature          | -30  | 85   | °C   |                                             |

| T <sub>STRG</sub>    | Storage Temperature Range              | -40  | 85   | °C   |                                             |

| T <sub>BODY</sub>    | Package Body Temperature               |      | 260  | °C   | IPC/JEDEC J-STD-020 <sup>(1)</sup>          |

| RH <sub>NC</sub>     | Relative Humidity (non-<br>condensing) | 5    | 85   | %    |                                             |

| MSL                  | Moisture Sensitivity Level             |      | 3    |      | Maximum floor life time of 168h             |

(1) The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pbfree leaded packages is "Matte Tin" (100% Sn)

## **5** Electrical Characteristics

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. All voltages with respect to GND/PGND. Device parameters are guaranteed at VDD=1.8 V and  $T_A=25$  °C unless otherwise noted.

Figure 6:

**Electrical Characteristics of AS7343**

| Symbol       | Parameter                                     | Conditions                                                     | Min  | Тур | Max  | Unit   |

|--------------|-----------------------------------------------|----------------------------------------------------------------|------|-----|------|--------|

| VDD          | Supply Voltage                                |                                                                | 1.7  | 1.8 | 1.98 | V      |

| ТА           | Operating free-air temperature <sup>(1)</sup> |                                                                | -30  | 25  | 85   | °C     |

| Power Consur | nption                                        |                                                                |      |     |      |        |

|              |                                               | VDD=1.8 V; T <sub>A</sub> =25 °C<br>Active mode <sup>(3)</sup> |      | 210 | 280  | μA     |

| IDD          | Supply Current <sup>(2)</sup>                 | VDD=1.8 V; T <sub>A</sub> =25 °C<br>Idle mode <sup>(4)</sup>   |      | 40  | 60   | μA     |

|              |                                               | VDD=1.8 V; T <sub>A</sub> =25 °C<br>Sleep mode <sup>(5)</sup>  |      | 0.7 | 5    | μA     |

| Digital Pins |                                               |                                                                |      |     |      |        |

| VIH          | SCL,SDA input high voltage                    |                                                                | 1.26 |     |      | V      |

| VIL          | SCL,SDA input low voltage                     |                                                                |      |     | 0.54 | V      |

| VOL          | INT, SDA output low voltage                   | 6 mA sink current                                              |      |     | 0.4  | V      |

| CI           | Input pin capacitance                         |                                                                |      |     | 10   | pF     |

| lleak        | Leakage current into<br>SCL,SDA,INT pins      |                                                                | -5   |     | 5    | μA     |

| GPIO         |                                               |                                                                |      |     |      |        |

| CLOAD        | Maximum capacitive<br>load GPIO               |                                                                |      |     | 20   | pF     |

| LED Driver   |                                               |                                                                |      |     |      |        |

|              |                                               | I_LDR= 4 mA ; LED_HALF = "0"                                   |      |     | 240  | ~~\/   |

| V_LDR        |                                               | I_LDR= 4 mA ; LED_HALF = "1"                                   |      |     | 130  | – mV   |

| V_LUK        | LDR compliance voltage                        | I LDR 134 mA ; LED_HALF = "0"                                  |      |     | 280  | – mV   |

|              |                                               | I LDR 134 mA ; LED_HALF = "1"                                  | _    |     | 180  | - 111V |

(1) While the device is operational across the temperature range, functionality will vary with temperature.

(2) Supply current values are shown at the VDD pin and do not include current through pin LDR.

(3) Active state occurs during active integration. (PON = "1"; SP\_EN = "1") If wait is enabled (WEN = "1"), supply current is lower during the wait period

(4) Idle state occurs when PON = "1" and all functions are disabled

(5) Sleep state occurs when PON = "0" and I<sup>2</sup>C bus is idle. If I<sup>2</sup>C traffic is active device automatically enters idle mode.

### 顶点光电子商城 https://www.vertex-icbuy.com/

## **6 Optical Characteristics**

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. All voltages with respect to GND/PGND. Device parameters are guaranteed at VDD=1.8 V and  $T_A=25$  °C unless otherwise noted.

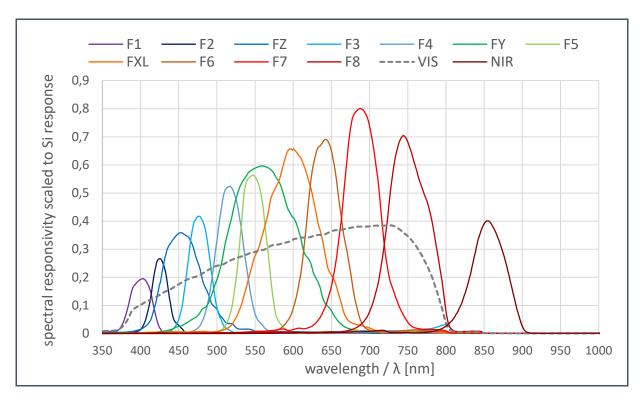

#### Figure 7:

AS7343 Optical Channel Summary

| Channel | Peak  | Wavelength [nm | Full Width Half Maximum [nm] |       |  |

|---------|-------|----------------|------------------------------|-------|--|

| Channel | (min) | λp (typ)       | (max)                        | (typ) |  |

| F1      | 395   | 405            | 415                          | 30    |  |

| F2      | 415   | 425            | 435                          | 22    |  |

| FZ      | 440   | 450            | 460                          | 55    |  |

| F3      | 465   | 475            | 485                          | 30    |  |

| F4      | 505   | 515            | 525                          | 40    |  |

| FY      | 545   | 555            | 565                          | 100   |  |

| F5      | 540   | 550            | 560                          | 35    |  |

| FXL     | 590   | 600            | 610                          | 80    |  |

| F6      | 630   | 640            | 650                          | 50    |  |

| F7      | 680   | 690            | 700                          | 55    |  |

| F8      | 735   | 745            | 755                          | 60    |  |

| NIR     | 845   | 855            | 865                          | 54    |  |

(1) Parameter measured on a production ongoing sample bases on glass using diffused light. The table above is valid for full sensor response including diffuser, package and photodiode response.

(2) Peak Wavelength is validated by smoothed/averaged monochromator measurement data.

#### Figure 8:

Optical Characteristics of Spectral Channels, AGAIN: 1024x, Integration Time: 27.8 ms

| Symbol             | Parameter                                 | Conditions                                              | Min  | Тур   | Max   | Unit   |

|--------------------|-------------------------------------------|---------------------------------------------------------|------|-------|-------|--------|

| Re_F1              | Irradiance<br>responsivity<br>channel F1  | LED_396nm ; Ee= 155 mW/m²<br>LED_408 nm ; Ee= 155 mW/m² | 4311 | 5749  | 7186  | counts |

| R <sub>e_F2</sub>  | Irradiance<br>responsivity<br>channel F2  | LED_408nm ; Ee= 155 mW/m²<br>LED_448nm ; Ee= 155 mW/m²  | 1317 | 1756  | 2196  | counts |

| R <sub>e_FZ</sub>  | Irradiance<br>responsivity<br>channel FZ  | LED_428nm ; Ee= 155 mW/m²<br>LED_480nm ; Ee= 155 mW/m²  | 1627 | 2169  | 2711  | counts |

| R <sub>e_F3</sub>  | Irradiance<br>responsivity<br>channel F3  | LED_448nm ; Ee= 155 mW/m²<br>LED_500nm ; Ee= 155 mW/m²  | 577  | 770   | 962   | counts |

| Re_F4              | Irradiance<br>responsivity<br>channel F4  | LED_500nm ; Ee= 155 mW/m²<br>LED_534nm ; Ee= 155 mW/m²  | 2356 | 3141  | 3926  | counts |

| Re_FY              | Irradiance<br>responsivity<br>channel FY  | LED_534nm ; Ee= 155 mW/m²<br>LED_593nm ; Ee= 155 mW/m²  | 2810 | 3747  | 4684  | counts |

| R <sub>e_F5</sub>  | Irradiance<br>responsivity<br>channel F5  | LED_531nm ; Ee= 155 mW/m²<br>LED_594nm ; Ee= 155 mW/m²  | 1180 | 1574  | 1967  | counts |

| Re_FXL             | Irradiance<br>responsivity<br>channel FXL | LED_593nm ; Ee= 155 mW/m²<br>LED_628nm ; Ee= 155 mW/m²  | 3582 | 4776  | 5970  | counts |

| R <sub>e_F6</sub>  | Irradiance<br>responsivity<br>channel F6  | LED_618nm ; Ee= 155 mW/m²<br>LED_665nm ; Ee= 155 mW/m²  | 2502 | 3336  | 4170  | counts |

| R <sub>e_F7</sub>  | Irradiance<br>responsivity<br>channel F7  | LED_685nm ; Ee= 155 mW/m²<br>LED_715nm ; Ee= 155 mW/m²  | 4095 | 5435  | 6774  | counts |

| R <sub>e_F8</sub>  | Irradiance<br>responsivity<br>channel F8  | LED_715nm ; Ee= 155 mW/m²<br>LED_766nm ; Ee= 155 mW/m²  | 648  | 864   | 1080  | counts |

| R <sub>e_NIR</sub> | Irradiance<br>responsivity<br>channel NIR | LED_849nm ; Ee= 155 mW/m²<br>LED_903nm ; Ee= 155 mW/m²  | 7936 | 10581 | 13226 | counts |

#### Figure 9:

Optical Characteristics of Broadband Channels, AGAIN: 1024x, FD\_GAIN: 64x, Integration Time: 27.8 ms

| Symbol             | Parameter                                     | Conditions                                                                   | Min  | Тур  | Max  | Unit   |

|--------------------|-----------------------------------------------|------------------------------------------------------------------------------|------|------|------|--------|

| R <sub>e_FD</sub>  | Irradiance<br>responsivity<br>channel Flicker | LED_593nm ; Ee= 155 mW/m²<br>LED_766nm ; Ee= 155 mW/m²<br>FD_GAIN=64x        | 3233 | 4311 | 5389 | counts |

| R <sub>e_VIS</sub> | Irradiance<br>responsivity<br>channel VIS     | LED_396nm ; Ee= 155 mW/m²<br>LED_766nm ; Ee= 155 mW/m²<br>2 VIS PDs read-out | 749  | 999  | 1248 | counts |

### Figure 10:

Optical Characteristics of AS7343, AGAIN: 128x, Integration Time: 11 ms (unless otherwise noted)

| Symbol                       | Parameter                                                                   | Conditions                                                                  | Min   | Тур   | Мах   | Unit                |

|------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-------|-------|---------------------|

| Dark_1 <sup>(1)</sup>        | Dark ADC count value                                                        | Ee = 0 $\mu$ W/cm <sup>2</sup><br>AGAIN: 512x<br>Integration time:<br>98 ms |       | 0     | 5     | counts              |

|                              |                                                                             | AGAIN: 0.5x                                                                 | 7.49  | 7.9   | 8.28  |                     |

|                              |                                                                             | AGAIN: 1x                                                                   | 15    | 15.8  | 16.5  |                     |

|                              |                                                                             | AGAIN: 2x                                                                   | 30    | 31.6  | 33.2  | See                 |

|                              |                                                                             | AGAIN: 4x                                                                   | 61    | 64    | 67    | note <sup>(3)</sup> |

|                              | Gain <sup>(2)</sup> Optical gain ratios,<br>relative to 64x gain<br>setting | AGAIN: 8x                                                                   | 117   | 124   | 130   |                     |

|                              |                                                                             | AGAIN: 16x                                                                  | 235   | 247   | 259   |                     |

| Gain <sup>(2)</sup><br>ratio |                                                                             | AGAIN: 32x                                                                  | 0.475 | 0.5   | 0.525 |                     |

|                              |                                                                             | AGAIN: 64x                                                                  |       | 1     |       |                     |

|                              |                                                                             | AGAIN: 128x                                                                 | 1.9   | 2     | 2.1   |                     |

|                              |                                                                             | AGAIN: 256x                                                                 | 3.9   | 4.1   | 4.3   |                     |

|                              |                                                                             | AGAIN: 512x                                                                 | 8.1   | 8.6   | 9.1   |                     |

|                              |                                                                             | AGAIN: 1024x                                                                | 15.2  | 16.9  | 18.6  |                     |

|                              |                                                                             | AGAIN: 2048x                                                                | 28.2  | 34.75 | 41.3  |                     |

| ADC<br>noise <sup>(4)</sup>  |                                                                             | White LED, 2700 K<br>Integration time:<br>100 ms                            |       | 0.05  |       | % full<br>scale     |

| t <sub>int</sub>             | Typical integration time <sup>(5)</sup>                                     | ASTEP = 599<br>ATIME = 29                                                   |       | 50    |       | ms                  |

| <b>t</b> ASTEP               | Integration time step size                                                  | ASTEP = 999                                                                 |       | 2.78  |       | ms                  |

| h <sub>ca</sub>              | Half cone angle                                                             | On the sensor                                                               |       | 40    |       | deg                 |

(1) The typical 3-sigma distribution is between 0 and 1 counts for AGAIN setting of 16x.

(2) The gain ratios are relative to 64x gain setting and are calculated relative to the response with integration time: 11 ms and AGAIN: 128x.

(3) ADC noise is calculated as the standard deviation of relative to full scale.

(4) Integration time, in milliseconds, is equal to: (ATIME + 1) x (ASTEP + 1) x 2.78 µs

(5) AGAIN ratio 0.5x to 16x is multiplied by 1000 for easier readability

## amu

## 7 Typical Operating Characteristics

### Figure 11:

Spectral Responsivity

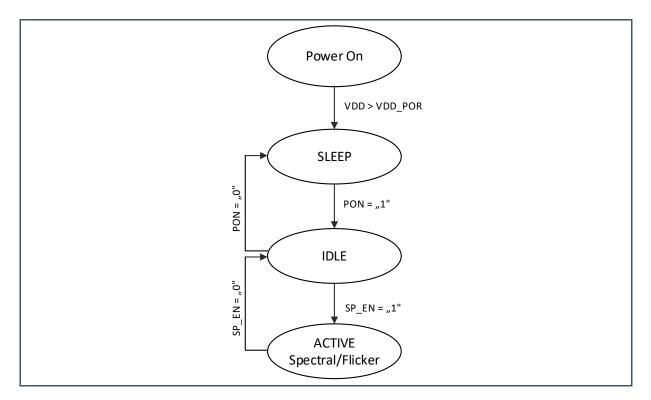

## 8 **Functional Description**

Upon power-up (POR), the device initializes. During initialization (typically 200 µs), the device will deterministically send NAK on I<sup>2</sup>C and cannot accept I<sup>2</sup>C transactions. All communication with the device must be delayed and all outputs from the device must be ignored including interrupts. After initialization, the device enters the SLEEP state. In this operational state, the internal oscillator and other circuitry are not active, resulting in ultra-low power consumption. If an I<sup>2</sup>C transaction occurs during this state, the I<sup>2</sup>C core wakes up temporarily to service the communication. Once the Power ON bit, "PON", is enabled, the device enters the IDLE state in which the internal oscillator and attendant circuitry are active, but power consumption remains low. Whenever the spectral measurement is enabled (SP\_EN = "1") the device enters the ACTIVE state. If the spectral measurement is disabled (SP\_EN = "0") the device returns to the IDLE state. The figure below describes a simplified state diagram and the typical supply currents in each state.

If Sleep after Interrupt is enabled (SAI = "1" in register 0xAC), the state machine will enter SLEEP when an interrupt occurs. Entering SLEEP does not automatically change any of the register settings (e.g. PON bit is still high, but the normal operational state is over-ridden by SLEEP state). SLEEP state is terminated when the SAI\_ACTIVE bit is cleared (the status bit is in register 0xA7 and the clear status bit is in register 0xFA).

Figure 12: Simplified State Diagram

### 8.1 Device Architecture

The device features six independent 16-bit ADCs. Gain and integration time of the six ADCs can be adjusted with the I<sup>2</sup>C interface. A wait time can be programed to automatically set a delay between two consecutive spectral measurements and to reduce overall power consumption. Once a measurement is started, the device is automatically processing the channels and storing the measurement data on chip

Figure 13: Simplified Block Diagram

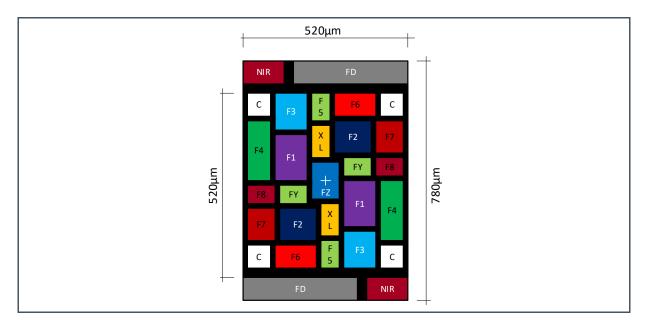

### 8.2 Sensor Array

The device features a 5x5-photodiode array. On top and below the photodiode array there are two photodiodes with dedicated functions such as flicker detection ("FD") and near- infrared response ("NIR"). The photodiode "C" represents a photodiode without filter and is responsive in the visible spectral range. ("VIS").

Figure 14: Sensor Array

### 8.3 GPIO

The GPIO can be used synchronization input to start/stop the spectral measurement. It also allows synchronizing the LED driver (LDR) with an external start/stop signal. Default state of the GPIO is "output".

### 8.4 Interrupt (INT)

The interrupt (INT) can be used to define thresholds and read-out the device only when the channel threshold has been reached. The pin is active low.

### 8.5 LED Driver (LDR)

The LED driver is programmable and can be used to drive external LEDs. It is also possible to synchronize the LED driver with an external start/stop signal via pin GPIO.

### 顶点光电子商城 https://www.vertex-icbuy.com/

## 9 I<sup>2</sup>C Interface

The device uses I<sup>2</sup>C serial communication protocol for communication. The device supports 7-bit chip addressing and both standard and full-speed clock frequency modes. Read and Write transactions comply with the standard set by Philips (now NXP). Internal to the device, an 8-bit buffer stores the register address location of the desired byte to read or write. This buffer auto-increments upon each byte transfer and is retained between transaction events (i.e. valid even after the master issues a STOP command and the I<sup>2</sup>C bus is released). During consecutive Read transactions, the future/repeated I<sup>2</sup>C Read transaction may omit the memory address byte normally following the chip address byte; the buffer retains the last register address +1. All 16-bit fields have a latching scheme for reading and writing. In general, it is recommended to use I<sup>2</sup>C bursts whenever possible, especially in this case when accessing two bytes of one logical entity. When reading these fields, the low byte must be read first, and it triggers a 16-bit latch that stores the 16-bit field. The high byte must be read immediately afterwards. When writing to these fields, the low byte must be written first, immediately followed by the high byte. Reading or writing to these registers without following these requirements will cause errors.

### 9.1 I<sup>2</sup>C Address

Figure 15: AS7343 I<sup>2</sup>C Slave Address

| Device  | I <sup>2</sup> C Address |

|---------|--------------------------|

| AS7343  | 0x39                     |

| AS7343B | 0x29                     |

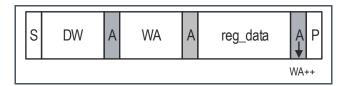

### 9.2 I<sup>2</sup>C Write Transaction

A Write transaction consists of a START, CHIP-ADDRESSWRITE, REGISTER-ADDRESS WRITE, DATA BYTE(S), and STOP (P). Following each byte (9TH clock pulse) the slave places an ACKNOWLEDGE/NOT- ACKNOWLEDGE (A/N) on the bus. If the slave transmits N, the master may issue a STOP.

Figure 16: I<sup>2</sup>C Byte Write

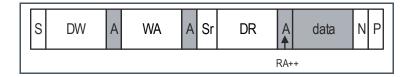

### 9.3 I<sup>2</sup>C Read Transaction

A Read transaction consists of a START, CHIP-ADDRESSWRITE, REGISTER-ADDRESS, RESTART, CHIP-ADDRESSREAD, DATA BYTE(S), and STOP. Following all but the final byte the master places an ACK on the bus (9TH clock pulse). Termination of the Read transaction is indicated by a NACK being placed on the bus by the master, followed by STOP.

Figure 17: I<sup>2</sup>C Read

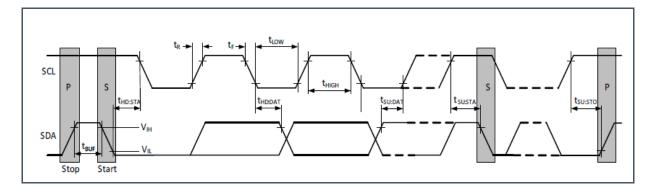

### 9.4 Timing Characteristics

Figure 18: I<sup>2</sup>C Timing Characteristics

| Symbol  | Parameter                                                                                       | Min | Тур | Max | Unit |

|---------|-------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| fscl    | I <sup>2</sup> C clock frequency                                                                |     |     | 1   | MHz  |

| tBUF    | Bus free time between start and stop condition                                                  | 1.3 |     |     |      |

| ths;sta | Hold time after (repeated) start condition.<br>After this period, the first clock is generated. | 0.6 |     |     | μs   |

## amu

| Symbol         | Parameter                           | Min | Тур | Max | Unit |

|----------------|-------------------------------------|-----|-----|-----|------|

| tsu;sta        | Repeated start condition setup time | 0.6 |     |     |      |

| tsu;sto        | Stop condition setup time           | 0.6 |     |     |      |

| tLOW           | SCL clock low period                | 1.3 |     |     |      |

| tніgн          | SCL clock high period               | 0.6 |     |     |      |

| thd;dat        | Data hold time                      | 0   |     |     |      |

| tsu;dat        | Data setup time                     | 100 |     |     | 20   |

| tF             | Clock/data fall time                |     |     | 300 | ns   |

| t <sub>R</sub> | Clock/data rise time                |     |     | 300 |      |

## 9.5 Timing Diagrams

Figure 19: I<sup>2</sup>C Slave Timing Diagram

## **10** Register Description

The device is controlled and monitored by registers accessed through the I<sup>2</sup>C serial interface. These registers provide device control functions and can be read to determine device status and acquire device data.

The register set is summarized below. The values of all registers and fields that are listed as reserved or are not listed must not be changed at any time. Two-byte fields are always latched with the low byte followed by the high byte. The "Name" column illustrates the purpose of each register by highlighting the function associated to each bit. The bits are shown from MSB (D7) to LSB (D0). GRAY fields are reserved and their values must not be changed at any time.

In order to access registers from 0x58 to 0x66 bit REG\_BANK in register CFG0 (0xBF) needs to be set to "1". For register access of registers 0x80 and above bit REG\_BANK needs to be set to "0".

### 10.1 Register Overview

Figure 20: Register Overview

| Addr | Name    | <d7></d7>       | <d6></d6> | <d5></d5> | <d4></d4>  | <d3></d3>   | <d2></d2> | <d1></d1>   | <d0></d0> |

|------|---------|-----------------|-----------|-----------|------------|-------------|-----------|-------------|-----------|

| 0x58 | AUXID   |                 |           |           |            |             | AUXID     | [3:0]       |           |

| 0x59 | REVID   |                 |           |           |            |             | F         | REVID [2:0] |           |

| 0x5A | ID      |                 |           |           | ID         | [7:0]       |           |             |           |

| 0x66 | CFG12   |                 |           |           |            |             | SF        | P_TH_CH [   | 2:0]      |

| 0x80 | ENABLE  |                 | FDEN      |           | SMUXE<br>N | WEN         |           | SP_EN       | PON       |

| 0x81 | ATIME   |                 |           |           | ATIM       | 1E [7:0]    |           |             |           |

| 0x83 | WTIME   |                 |           |           | WTIN       | /IE [7:0]   |           |             |           |

| 0x84 |         |                 |           |           | SP_TH_I    | LSB [7:0]   |           |             |           |

| 0x85 | SP_TH_L |                 |           |           | SP_TH_L    | _MSB [7:0]  |           |             |           |

| 0x86 |         |                 |           |           | SP_TH_H    | H_LSB [7:0] |           |             |           |

| 0x87 | SP_TH_H |                 |           |           | SP_TH_H    | I_MSB [7:0] |           |             |           |

| 0x93 | STATUS  | ASAT            |           |           |            | AINT        | FINT      |             | SINT      |

| 0x94 | ASTATUS | ASAT_<br>STATUS |           |           |            |             | AGAIN_STA | TUS [3:0]   |           |

| 0x95 |         |                 |           |           | DATA_      | _0_L [7:0]  |           |             |           |

| 0x96 | DATA_0  |                 |           |           | DATA_      | _0_H [7:0]  |           |             |           |

| 0x97 | DATA 1  |                 |           |           | DATA_      | _1_L [7:0]  |           |             |           |

| 0x98 | DATA_I  |                 |           |           | DATA_      | 1_H [7:0]   |           |             |           |

| 0x99 | DATA_2  |                 |           |           | DATA_      | _2_L [7:0]  |           |             |           |

## amu

| Addr | Name     | <d7></d7>   | <d6></d6> | <d5></d5>     | <d4></d4>    | <d3></d3>    | <d2></d2>     | <d1></d1>     | <d0></d0>     |

|------|----------|-------------|-----------|---------------|--------------|--------------|---------------|---------------|---------------|

| 0x9A |          |             |           |               | DATA_        | _2_H [7:0]   |               |               |               |

| 0x9B |          |             |           |               | DATA_        | _3_L [7:0]   |               |               |               |

| 0x9C | DATA_3   |             |           |               | DATA_        | _3_H [7:0]   |               |               |               |

| 0x9D |          |             |           |               | DATA_        | _4_L [7:0]   |               |               |               |

| 0x9E | DATA_4   |             |           |               | DATA_        | _4_H [7:0]   |               |               |               |

| 0x9F |          |             |           |               | DATA_        | _5_L [7:0]   |               |               |               |

| 0xA0 | DATA_5   |             |           |               | DATA_        | _5_H [7:0]   |               |               |               |

| 0xA1 |          |             |           |               | DATA_        | _6_L [7:0]   |               |               |               |

| 0xA2 | DATA_6   |             |           |               | DATA_        | _6_H [7:0]   |               |               |               |

| 0xA3 |          |             |           |               | DATA_        | _7_L [7:0]   |               |               |               |

| 0xA4 | DATA_7   |             |           |               | DATA_        | _7_H [7:0]   |               |               |               |

| 0xA5 |          |             |           |               | DATA_        | _8_L [7:0]   |               |               |               |

| 0xA6 | DATA_8   |             |           |               | DATA_        | _8_H [7:0]   |               |               |               |

| 0xA7 |          |             |           |               | DATA_        | _9_L [7:0]   |               |               |               |

| 0xA8 | DATA_9   |             |           |               | DATA_        | _9_H [7:0]   |               |               |               |

| 0xA9 |          |             |           |               | DATA_        | 10_L [7:0]   |               |               |               |

| 0xAA | DATA_10  |             |           |               | DATA_        | 10_H [7:0]   |               |               |               |

| 0xAB |          |             |           |               | DATA_        | 11_L [7:0]   |               |               |               |

| 0xAC | DATA_11  |             |           |               | DATA_        | 11_H [7:0]   |               |               |               |

| 0xAD |          |             |           |               | DATA_        | 12_L [7:0]   |               |               |               |

| 0xAE | DATA_12  |             |           |               | DATA_        | 12_H [7:0]   |               |               |               |

| 0xAF |          |             |           |               | DATA_        | 13_L [7:0]   |               |               |               |

| 0xB0 | DATA_13  |             |           |               | DATA_        | 13_H [7:0]   |               |               |               |

| 0xB1 |          |             |           |               | DATA_        | 14_L [7:0]   |               |               |               |

| 0xB2 | DATA_14  |             |           |               | DATA_        | 14_H [7:0]   |               |               |               |

| 0xB3 |          |             |           |               | DATA_        | 15_L [7:0]   |               |               |               |

| 0xB4 | DATA_15  |             |           |               | DATA_        | 15_H [7:0]   |               |               |               |

| 0xB5 |          |             |           |               | DATA_        | 16_L [7:0]   |               |               |               |

| 0xB6 | DATA_16  |             |           |               | DATA_        | 16_H [7:0]   |               |               |               |

| 0xB7 |          |             |           |               | DATA_        | 17_L [7:0]   |               |               |               |

| 0xB8 | DATA_17  |             |           |               | DATA_        | 17_H [7:0]   |               |               |               |

| 0x90 | STATUS 2 |             | AVALID    |               | ASAT_<br>DIG | ASAT_<br>ANA |               | FDSAT<br>_ANA | FDSAT_<br>DIG |

| 0x91 | STATUS 3 |             |           | INT_SP_H      | INT_SP<br>_L |              |               |               |               |

| 0xBB | STATUS 5 |             |           |               |              | SINT<br>_FD  | SINT<br>_SMUX |               |               |

| 0xBC | STATUS 4 | FIFO_<br>OV |           | OVTEMP        | FD_TRI<br>G  |              | SP_TRIG       | SAI_<br>ACT   | INT_BUS<br>Y  |

| 0xBF | CFG 0    |             |           | LOW_<br>POWER | REG_<br>BANK |              | WLONG         |               |               |

## amu

| Addr | Name             | <d7></d7>             | <d6></d6>   | <d5></d5>     | <d4></d4>     | <d3></d3>              | <d2></d2>              | <d1></d1>    | <d0></d0>         |

|------|------------------|-----------------------|-------------|---------------|---------------|------------------------|------------------------|--------------|-------------------|

| 0xC6 | CFG1             |                       |             |               |               |                        | AGAIN[4:0]             |              |                   |

| 0xC7 | CFG3             |                       |             |               | SAI           |                        |                        |              |                   |

| 0xF5 | CFG6             |                       |             |               |               | MUX_<br>MD[4:3]        |                        |              |                   |

| 0xC9 | CFG8             | FIFO_TH [             | [7:6]       |               |               |                        |                        |              |                   |

| 0xCA | CFG9             |                       | SIEN<br>_FD |               | SIEN<br>_SMUX |                        |                        |              |                   |

| 0x65 | CFG10            |                       |             |               |               |                        | F                      | D_PERS [2    | 2:0]              |

| 0xCF | PERS             |                       |             |               |               |                        | APERS                  | [3:0]        |                   |

| 0x6B | GPIO             |                       |             |               |               | GPIO_<br>INV           | GPIO_<br>IN_EN         | GPIO_<br>OUT | GPIO_<br>IN       |

| 0xD4 | ASTEP            |                       |             |               | ASTI          | EP [7:0]               |                        |              |                   |

| 0xD5 | ASTEP            |                       |             |               | ASTE          | EP [15:8]              |                        |              |                   |

| 0xD6 | CFG20            | FD_FIF<br>O_8b        | auto_       | _SMUX         |               |                        |                        |              |                   |

| 0xCD | LED              | LED_AC<br>T           |             |               | L             | ED_DRIVE [6:0]         | ]                      |              |                   |

| 0xD7 | AGC_GAIN_<br>MAX |                       | AGC_FD_G    | AIN_MAX [7:4] |               |                        |                        |              |                   |

| 0xDE | AZ_CONFIG        |                       |             |               | AT_NTH_IT     | ERATION [7:0]          |                        |              |                   |

| 0xE0 | FD_TIME_1        |                       |             |               | FD_T          | IME [7:0]              |                        |              |                   |

| 0xE2 | FD_TIME_2        |                       |             | FD_GAIN [7:   | 3]            |                        | FD                     | D_TIME [10   | :8]               |

| 0xDF | FD_CFG0          | FIFO_W<br>RITE_F<br>D |             |               |               |                        |                        |              |                   |

| 0xE3 | FD_STATUS        |                       |             | FD_<br>VALID  | FD_<br>SAT    | FD_<br>120HZ_<br>VALID | FD_<br>100Hz_<br>VALID | FD_<br>120Hz | FD_<br>100Hz      |

| 0xF9 | INTENAB          | ASIEN                 |             |               |               | SP_IEN                 | FIEN                   |              | SIEN              |

| 0xFA | CONTROL          |                       |             |               |               | SW_<br>RESET           | SP_MAN<br>_AZ          | FIFO_<br>CLR | CLEAR_<br>SAI_ACT |

| 0xFC | FIFO_MAP         |                       | FIF         | O_WRITE_CH    | 15_DATA –     | FIFO_WRITE_C           | H0_DATA [6             | :1]          | ASTATU<br>S       |

| 0xFD | FIFO_LVL         |                       |             |               | FIFO_         | LVL [7:0]              |                        |              |                   |

| 0xFE | FDATA            |                       |             |               | FDAT          | A _L[7:0]              |                        |              |                   |

| 0xFF | IDATA            |                       |             |               | FDATA         | A_H [15:8]             |                        |              |                   |

### 10.2 Detailed Register Description

For easier readability, the detailed register description is done in groups of registers related to dedicated device functions. This is not necessarily related to its register address.

Explanation of register access abbreviations: RW = read or write R = read only W = write only SC = self-clearing after access

### 10.2.1 Enable and Configuration Registers

The following registers are needed to power up and configure the device. To operate the device set bit PON = "1" first (register 0x80) after that configure the device and enable interrupts before setting  $SP_EN = "1"$ . Changing configuration while  $SP_EN = "1"$  may result in invalid results.

#### ENABLE Register (Address 0x80)

Figure 21: ENABLE Register

| Addr: | 0x80     | ENABLE  |        |                                                                                                                                                                                           |

|-------|----------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit Name | Default | Access | Bit Description                                                                                                                                                                           |

| 7     | Reserved | 0       | RW     | Reserved                                                                                                                                                                                  |

| 6     | FDEN     | 0       | RW     | Flicker Detection Enable.<br>0: Flicker Detection disabled<br>1: Flicker Detection enabled                                                                                                |

| 5     | Reserved | 0       | RW     | Reserved                                                                                                                                                                                  |

| 4     | SMUXEN   | 0       | RW     | <ul><li>SMUX Enable.</li><li>1: Starts SMUX command</li><li>Note: This bit gets cleared automatically as soon as SMUX operation is finished</li></ul>                                     |

| 3     | WEN      | 0       | RW     | <ul> <li>Wait Enable.</li> <li>0: Wait time between two consecutive spectral measurements disabled</li> <li>1: Wait time between two consecutive spectral measurements enabled</li> </ul> |

| 2     | Reserved | 0       | RW     | Reserved                                                                                                                                                                                  |

| 1     | SP_EN    | 0       | RW     | Spectral Measurement Enable.<br>0: Spectral Measurement Disabled<br>1: Spectral Measurement Enabled                                                                                       |

| Addr: | 08x0     | ENABLE  |        |                                                                                                       |

|-------|----------|---------|--------|-------------------------------------------------------------------------------------------------------|

| Bit   | Bit Name | Default | Access | Bit Description                                                                                       |

|       |          |         |        | Power ON.                                                                                             |

| 0     | PON      | 0       | RW     | 0: AS7343 disabled                                                                                    |

| 0     | FON      | 0       |        | 1: AS7343 enabled                                                                                     |

|       |          |         |        | Note: When bit is set, internal oscillator is activated, allowing timers and ADC channels to operate. |

### GPIO Register (Address 0x6B)

### Figure 22: GPIO Register

| Addr: | 0x6B       | GPIO    | GPIO   |                                                                                |  |

|-------|------------|---------|--------|--------------------------------------------------------------------------------|--|

| Bit   | Bit Name   | Default | Access | Bit Description                                                                |  |

| 7:4   | Reserved   | 0       |        | Reserved                                                                       |  |

| 3     | GPIO_INV   | 0       | RW     | GPIO Invert.<br>If set, the GPIO output is inverted.                           |  |

| 2     | GPIO_IN_EN | 0       | RW     | GPIO Input Enable.<br>If set, the GPIO pin accepts a non-floating input.       |  |

| 1     | GPIO_OUT   | 1       | RW     | GPIO Output.<br>If set, the output state of the GPIO is active directly.       |  |

| 0     | GPIO_IN    | 0       | R      | GPIO Input.<br>Indicates the status of the GPIO input if<br>GPIO_IN_EN is set. |  |

### LED Register (Address 0xCD)

Figure 23: LED Register

| Addr: | 0xCD      | LED      |        |                                                               |

|-------|-----------|----------|--------|---------------------------------------------------------------|

| Bit   | Bit Name  | Default  | Access | Bit Description                                               |

| 7     | LED_ACT   | 0        | RW     | LED Control.<br>0: External LED connected to pin LDR off      |

|       |           |          |        | 1: External LED connected to pin LDR on LED Driving Strength. |

| 0.0   |           | 000.0400 |        | 000 0000: 4 mA<br>000 0001: 6 mA                              |

| 6:0   | LED_DRIVE | 000 0100 | RW     | 000 0010: 8 mA<br>000 0011: 10 mA                             |

|       |           |          |        | 000 0100: 12 mA                                               |

| Addr: | 0xCD     | LED     |        |                  |  |

|-------|----------|---------|--------|------------------|--|

| Bit   | Bit Name | Default | Access | Bit Description  |  |

|       |          |         |        |                  |  |

|       |          |         |        | 111 1110: 256 mA |  |

|       |          |         |        | 111 1111: 258 mA |  |

#### INTENAB Register (Address 0xF9)

Figure 24: INTENAB Register

| Addr: | 0xF9     | INTENAB |        |                                                                                                                                                                                           |

|-------|----------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit Name | Default | Access | Bit Description                                                                                                                                                                           |

| 7     | ASIEN    | 0       | RW     | Spectral and Flicker Detect Saturation Interrupt<br>Enable.<br>When asserted permits saturation interrupts to be<br>generated.                                                            |

| 6:4   | Reserved |         |        | Reserved                                                                                                                                                                                  |

| 3     | SP_IEN   | 0       | RW     | <b>Spectral Interrupt Enable.</b><br>When asserted permits interrupts to be generated, subject to the spectral thresholds and persistence filter. Bit is mirrored in the ENABLE register. |

| 2     | F_IEN    | 0       | RW     | FIFO Buffer Interrupt Enable.<br>When asserted permits interrupt to be generated<br>when FIFO_LVL exceeds the FIFO threshold<br>condition.                                                |

| 1     | Reserved | 0       |        | Reserved                                                                                                                                                                                  |

| 0     | SIEN     |         | RW     | System Interrupt Enable.<br>When asserted permits system interrupts to be<br>generated. Indicates that flicker detection status has<br>changed or SMUX operation has finished.            |

#### CONTROL Register (Address 0xFA)

Figure 25: CONTROL Register

| Addr: | 0xFA      | CONTROL |        |                                                                    |

|-------|-----------|---------|--------|--------------------------------------------------------------------|

| Bit   | Bit Name  | Default | Access | Bit Description                                                    |

| 7:4   | Reserved  | 0       |        | Reserved                                                           |

| 3     | SW_RESET  | 0       | RW     | Software Reset<br>When set the device will force a power on reset. |

| 2     | SP_MAN_AZ | 0       | RW     | Spectral Engine Manual Autozero.                                   |

| Addr: | 0xFA          | CONTROL |        |                                                                                                                         |

|-------|---------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit Name      | Default | Access | Bit Description                                                                                                         |

|       |               |         |        | Starts a manual autozero of the spectral engines.<br>Set SP_EN = 0 before starting a manual autozero for<br>it to work. |

|       |               |         |        | FIFO Buffer Clear.                                                                                                      |

| 1     | FIFO_CLR      | 0       | RW     | Clears all FIFO data, FINT, FIFO_OV, and<br>FIFO_LVL.                                                                   |

|       |               |         |        | Clear Sleep-After-Interrupt Active.                                                                                     |

| 0     | CLEAR_SAI_ACT | 0       | RW     | Clears SAI_ACTIVE, ends sleep, and restarts device operation.                                                           |

### **10.2.2** ADC Timing Configuration / Integration Time

The integration time is set using the ATIME (0x81) and ASTEP (0xD4, 0xD5) registers. The integration time, in milliseconds, is equal to:

Equation 1: Setting the integration time

$t_{int} = (ATIME + 1) \times (ASTEP + 1) \times 2.78 \mu s$

It is not allowed that both settings -ATIME and ASTEP - are set to "0".

The integration time also defines the full-scale ADC value, which is equal to:

Equation 2: ADC full scale value<sup>1</sup>

$ADC_{fullscale} = (ATIME + 1) \times (ASTEP + 1)$

#### ATIME Register (Address 0x81)

Figure 26: ATIME Register

| Addr: | Addr: 0x81 ATIME |         |        |                                     |                                    |

|-------|------------------|---------|--------|-------------------------------------|------------------------------------|

| Bit   | Bit Name         | Default | Access | Bit Description                     | on                                 |

|       |                  |         |        | Integration time<br>Sets the number | of integration steps from 1 to 255 |

| 7:0   | ATIME            | 0x00    | RW     | Value                               | Integration Time                   |

|       |                  |         |        | 0                                   | ASTEP                              |

|       |                  |         |        | n                                   | ASTEP x (n+1)                      |

<sup>1</sup> The maximum ADC count is 65535. Any ATIME/ASTEP field setting resulting in higher ADC full-scale values would result in a full-scale of 65535.

| Addr: 0 | )x81     | ATIME   |        |                 |             |

|---------|----------|---------|--------|-----------------|-------------|

| Bit     | Bit Name | Default | Access | Bit Description |             |

|         |          |         |        | 255             | ASTEP x 256 |

#### ASTEP Register (Address 0xD4, 0xD5)

Figure 27: ASTEP Register

| Addr:          | 0xD4, 0xD5 | ASTEP   | ASTEP  |                                                                                                                              |                      |  |  |

|----------------|------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Bit            | Bit Name   | Default | Access | Bit Descriptio                                                                                                               | on                   |  |  |

| 7:0 ASTEP 0xCA |            |         |        | <b>Integration Time Step Size.</b><br>Sets the integration time per step in increments of 2.78 μs. The default value is 999. |                      |  |  |

|                | ASTEP 0xCA |         |        | VALUE                                                                                                                        | STEP SIZE            |  |  |

|                |            |         |        | 0                                                                                                                            | 2.78 µs              |  |  |

|                |            | 999     | RW     | n                                                                                                                            | 2.78 µs x (n+1)      |  |  |

|                |            |         |        | 599                                                                                                                          | 1.67 ms              |  |  |

|                |            |         |        | 999                                                                                                                          | 2.78 ms              |  |  |

| 15:8           | ASTEP 0xCB |         |        | 17999                                                                                                                        | 50 ms                |  |  |

|                |            |         |        | 65534                                                                                                                        | 182 ms               |  |  |

|                |            |         |        | 65535                                                                                                                        | Reserved, do not use |  |  |

#### WTIME Register (Address 0x83)

If wait is enabled (WEN = "1" register 0x80), each new measurement is started based on WTIME. It is necessary for WTIME to be sufficiently long for spectral integration and any other functions to be completed within the period. The device will warn the user if the timing is configured incorrectly. If WTIME is too short, then SP\_TRIG in register STATUS6 (ADDR: 0xA7) will be set to "1".

Figure 28: WTIME Register

| Addr: | 0x83     | WTIME   |        |               |                                                                      |            |

|-------|----------|---------|--------|---------------|----------------------------------------------------------------------|------------|

| Bit   | Bit Name | Default | Access | Bit Des       | cription                                                             |            |

| 7:0   | WTIME    | 0x00    | RW     | 8-bit value t | easurement Wait Tin<br>to specify the delay be<br>spectral measureme | etween two |

|       |          |         |        | Value         | Wait Cycles                                                          | Wait Time  |

|       |          |         |        | 0x00          | 1                                                                    | 2.78 ms    |

| Addr: | 0x83     | WTIME   |        |         |          |                 |

|-------|----------|---------|--------|---------|----------|-----------------|

| Bit   | Bit Name | Default | Access | Bit Des | cription |                 |

|       |          |         |        | 0x01    | 2        | 5.56 ms         |

|       |          |         |        | n       | n        | 2.78 ms x (n+1) |

|       |          |         |        | Oxff    | 256      | 711 ms          |

### FD\_TIME Register (Address 0xE0, 0xE2)

The register FD Time 1 and FD Time 2 can be used to configure the integration time and gain (ADC 5) of the flicker detection independently from the other ADCs. The FD\_TIME register is an 11-bit register with the MSB in register 0xDA (bit 10:8) and the LSB in register 0xD8 (bit 7:0). The bit FDEN (register 0x80) must be set to "1" in order to use the FD\_TIME registers. If the bit FDEN is not set, ADC5 runs automatically with the same gain and integration time as ADC0 to ADC4.

Equation 3: Calculating the flicker detection integration time

$t_{int FD} = FD_TIME \times 2.78 \mu s$

Figure 29: FD Time\_1 Register

| Addr: 0 | )xE0          | FD_TIME_ <sup>^</sup> | 1      |                                                                                                   |

|---------|---------------|-----------------------|--------|---------------------------------------------------------------------------------------------------|

| Bit     | Bit Name      | Default               | Access | Bit Description                                                                                   |

| 7:0     | FD_TIME [7:0] | 0110 0111             | RW     | LSB of flicker detection integration time. Note: must not be changed during FDEN = 1 and PON = 1. |

### Figure 30:

FD Time\_2 Register

| Addr: | Addr: 0xE2     |         | FD_TIME_2 |                                    |                                                                      |  |  |

|-------|----------------|---------|-----------|------------------------------------|----------------------------------------------------------------------|--|--|

| Bit   | Bit Name       | Default | Access    | Bit Description                    | on                                                                   |  |  |

|       |                |         |           | Flicker Detectio                   | n Gain Setting (ADC5)                                                |  |  |

|       |                |         |           | VALUE                              | GAIN                                                                 |  |  |

|       |                |         |           | 0                                  | 0.5x                                                                 |  |  |

|       |                |         |           | 1                                  | 1x                                                                   |  |  |

|       |                |         |           | 2                                  | 2x                                                                   |  |  |

|       |                |         |           | 3                                  | 4x                                                                   |  |  |

|       |                |         |           | 4                                  | 8x                                                                   |  |  |

| 7:3   | FD_GAIN        | 9       | RW        | 5                                  | 16x                                                                  |  |  |

|       |                |         |           | 6                                  | 32x                                                                  |  |  |

|       |                |         |           | 7                                  | 64x                                                                  |  |  |

|       |                |         |           | 8                                  | 128x                                                                 |  |  |

|       |                |         |           | 9                                  | 256x                                                                 |  |  |

|       |                |         |           | 10                                 | 512x                                                                 |  |  |

|       |                |         |           | 11                                 | 1024x                                                                |  |  |

|       |                |         |           | 12                                 | 2048x                                                                |  |  |

| 2:0   | FD_TIME [10:8] | 1       | RW        | MSB of flicker de not be changed o | tection integration time. Note: must<br>during FDEN = 1 and PON = 1. |  |  |

### **10.2.3** ADC Configuration

The following registers provide configuration for the 6 integrated ADCs (CH0 to CH5). It is possible to adjust the gain and setup the auto zero compensation for the ADCs.

#### CFG1 Register (Address 0xC6)

Figure 31: CFG1 Register

| Addr: 0xC6 |          | CFG1     | CFG1   |                                      |       |  |  |